Halbleiterfertigung mit KI und ML Von Chiplets bis Edge Computing: Wie sich eine Testbranche verändert

Anbieter zum Thema

Künstliche Intelligenz und maschinelles Lernen verbessern die Qualität und Effizienz in der Halbleiterfertigung. Testprozesse können optimiert werden und maschinelle Lernverfahren erkennen Muster und Anomalien, die Menschen nicht entdecken.

In der Halbleiterindustrie stehen KI und maschinelles Lernen (ML) im Mittelpunkt der Entwicklung, da neue Herstellungsverfahren und eine immer höhere Integrationsdichte die Halbleiterprüfung vor große Herausforderungen stellen. Die Halbleiterprüfindustrie ist gut positioniert, indem sie KI und ML zur Analyse und Korrelation von Daten entlang der gesamten Halbleiter-Wertschöpfungskette einsetzt. So können KI und ML die Halbleiterindustrie grundlegend verändern. Die Qualität und Effizienz im Halbleitertest steigen. Damit möglich sind eine neue Generation von KI-Prozessoren.

Diese KI-Prozessoren, die häufig von neuen Marktteilnehmern wie Hyperscalern und Start-ups entwickelt werden, sind allerdings nicht ganz unproblematisch. Dazu gehören die Verkleinerung der Prozessknoten, die komplexere Integration heterogener Einheiten, verbesserte Kommunikationsarchitekturen und der erhöhte Stromverbrauch und die daraus resultierende Wärmeentwicklung. Zu den Initiativen der Industrie gehören adaptive Echtzeittests, vorausschauende Wartung, Verbesserungen bei DC-Tests, thermische In-situ-Tests und -Optimierung sowie effiziente Arbeitsabläufe.

Neue Möglichkeiten mit den KI-Bausteinen

In der Pre-Chiplet-Ära waren traditionelle CPUs auf bestimmte Anwendungen ausgerichtet. Im Gegensatz dazu ermöglichen die neuen Chiplet-basierten KI-Bausteine Flexibilität für Anwendungen, die zum Zeitpunkt ihrer Entwicklung noch nicht bekannt waren. Die Teststrategien für diese Bausteine müssen genügend Daten generieren, um sie nach Abschluss der Tests neuen Anwendungen zuordnen zu können. In der traditionellen Testwelt besteht der Prüfling (DUT) aus einem Gehäuse mit einem oder wenigen Bauelementen, und der Tester muss direkten Zugriff auf die meisten Anschlüsse (Pins) des DUT haben. Jeder Testschritt, von der Post-Silicon-Validierung bis zum System-Level-Test, hat einen klar definierten Zweck und sammelt Testdaten.

Mit dem Übergang zu Chiplet-basierten Modulen, die eine Integration von CPU, GPU, Speicher und anderen Funktionen in einem einzigen 2,5D- oder 3D-Gehäuse ermöglichen, ändern sich die Anforderungen an die Testverfahren. Hier kann der Tester nur auf eine begrenzte Anzahl von Pins zugreifen. Daher muss der Tester in der Lage sein, bei jedem Testschritt wertvolle Daten zu extrahieren und zu nutzen, um sowohl den aktuellen Testschritt, als auch andere Design-, Fertigungs- und Testschritte zu optimieren.

Mit begrenztem Pin-Zugang muss der Tester Rückschlüsse auf die Vorgänge an nicht beobachtbaren Knoten ziehen. Ein zentraler Aspekt ist es, den Nutzen aus direkt erfassten Daten in allen Fertigungs- und Testschritten, einschließlich der Daten von On-Chip-Sensoren zu maximieren.

Effektive prädiktive und adaptive Testansätze

In der Chiplet-Welt müssen Tester dem System immer einen Schritt voraus sein. Beim Smart Pairing, einer Form des anwendungsbasierten Echtzeit-Binnings, werden Faktoren wie Spannung, Geschwindigkeit und Stromverbrauch berücksichtigt, um sicherzustellen, dass alle Chips in einem Paket kompatible elektrische und thermische Eigenschaften aufweisen. Dadurch werden Unterschiede in Bezug auf Zuverlässigkeit, Signalverzögerungen und Leistungsungleichgewichte minimiert. Regelbasierte Entscheidungsmodelle, die in der Pre-Chiplet-Welt funktionierten, erfüllen weiterhin bestimmte Zwecke.

In der Chiplet-Ära ist jedoch zusätzlich das ML-Modell entscheidend, um komplexe Echtzeit-Entscheidungsanforderungen zu erfüllen. Damit subtile Fehlermechanismen erkannt werden können, sind eine breite Palette an Eingabedaten notwendig. Außerdem werden mit begrenztem Testzugang im Endgehäuse On-Chip-Sensordaten, Geräteeinstellungen, Sensordaten sowie vorgelagerte Daten aus Entwicklung und Fertigung immer wichtiger. ML kann all diese Daten nutzen, um effektive prädiktive und adaptive Testansätze zu ermöglichen.

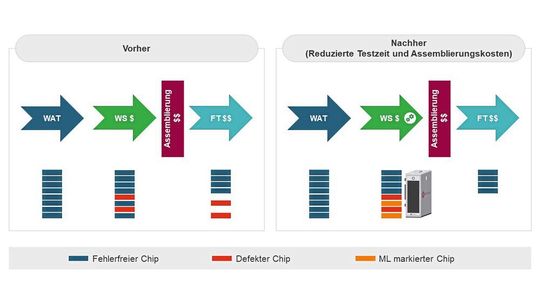

Wie ein vorgelagertes ML-Modell beim Packaging hilft

Ziel ist es, Fehler so früh wie möglich in der Testkette zu erkennen, bevor die Wafer zu verpackten Bauelementen montiert werden. In der Chiplet-/HI-Welt steigen die Kosten und die Komplexität des Packaging. Aus diesem Grund sollten nur 'known-good die' (KGD) in ein Gehäuse eingebaut werden. Ein vorgelagertes ML-Modell ermöglicht Echtzeit-Entscheidungen über KGDs auf der Basis von Daten aus mehreren Testschritten. Frühere Forschungen haben gezeigt, dass solche Methoden die Testkosten signifikant reduzieren können.

Es gibt jedoch Ausnahmen: Beispielsweise kann es vorteilhaft sein, einen langen Test von Packagingtest auf den Systemtest (System Level Test, SLT) zu verschieben, wo die Testzeit weniger kostspielig ist. Eine ML-Strategie kann helfen, den kompletten Testablauf zu optimieren. Während des gesamten Testprozesses ist es wichtig, KI und ML einzusetzen, um KI-Geräte zu testen, Testdaten zu analysieren, Daten über mehrere Wafer hinweg zu korrelieren und den Weg jedes Chips durch den Montageprozess genau zu verfolgen.

Verschiedene Werkzeuge und Algorithmen, die auf Design-, Fertigungs-, Test- und Gerätedaten angewendet werden, ermöglichen eine Korrelation über den gesamten Fertigungsprozess hinweg und liefern Erkenntnisse, die eine Optimierung des Prozesses ermöglichen.

Automatische Korrekturmaßnahmen während der Produktion

Steigende Testanforderungen erhöhen den Bedarf an KI- und ML-gestützten Vorhersagemethoden. Die Echtzeitausführung von Testcode ermöglicht automatische Korrekturmaßnahmen während der Produktion, um die Kosten unter Kontrolle zu halten. Ein Testkunde hat festgestellt, dass ML-basierte parametrische Vorhersagen die parametrische Testzeit um 50 Prozent oder mehr reduzieren und gleichzeitig erfolgreich leistungsangepasste Komponenten ohne Qualitätseinbußen identifizieren können.

Um sensibles geistiges Eigentum in ausgelagerten Produktionsumgebungen zu schützen, sind moderne Datensicherheitstechniken unerlässlich. Die Lieferkette für Halbleiter umfasst häufig Auftragsfertigung und Testdienstleistungen. Die Testgeräte in einer Einrichtung können Teile von mehreren IC-Lieferanten verarbeiten. In diesem Fall ist es für die Lieferanten nicht trivial, alle Aspekte der sensiblen Test-IP zu schützen. Von einer Einrichtung kann erwartet werden, dass sie ihre Umgebung schützt, aber in komplexen Lieferketten kann es schwierig sein, die Umgebung abzugrenzen.

KI/ML in Testumgebungen mit Edge Computing

Ein Ansatz ist das Zero-Trust-Sicherheitsmodell. Es bedeutet, dass Produkte und Dienste anderen Produkten und Diensten standardmäßig nicht vertrauen können. Eine Zero-Trust-Inferenzumgebung in Verbindung mit einem Testsystem schützt vor Bedrohungen sowohl innerhalb als auch außerhalb der traditionellen Netzwerkgrenzen, indem die 'Vertrauenszone' von der Netzwerkebene auf einzelne Knoten oder Anwendungen reduziert wird. Interaktionen zwischen Vertrauenszonen erfordern eine kontinuierliche Authentifizierung.

Die Ausführung von KI/ML-Workloads in einer Testumgebung muss zusätzlich zum eigentlichen Testablauf integriert werden und die Veränderungen in der Systemkonfiguration sind kostenintensiv. Edge Computing wird als eine effektive Lösung für Echtzeit-ML-Entscheidungen in der Testumgebung vorgeschlagen, da es niedrige Latenz, verbesserte Bandbreiteneffizienz, Skalierbarkeit sowie verbesserte Sicherheit und Datenschutz bietet. Es ermöglicht dynamisch adaptive Testabläufe, welche die Kosten des Tests (COT) minimieren und die Ausbeute maximieren.

Edge-Anwendungen für die Halbleiterfertigung mit KI/ML

Eine effektive Edge-Lösung sollte kompatibel mit verschiedenen Hardware- und Software-Plattformen sein, eine offene Architektur für Analysemodelle bieten und Erkenntnisse durch Integration aller Datenquellen über die gesamte Fertigungskette ermöglichen. Der Hersteller Advantest hat ACS RTDI eingeführt. Dabei handelt es sich um eine Plattform, die Halbleiter-Testdaten sammelt, analysiert, speichert und überwacht. Sie nutzt Edge Computing und Analysen mit geringer Latenz in einer Zero-Trust-Umgebung, um die Datennutzung zu rationalisieren und die Qualität, den Ertrag und die betriebliche Effizienz zu steigern.

Der ACS-Edge-HPC-Server arbeitet mit dem V93000 von Advantest und anderen ATE-Systemen zusammen, um rechenintensive Arbeitslasten zu verarbeiten. Das System V93000 ist flexibel bei der Prüfung verschiedener IC-Typen und unterstützt Instrumentenkarten für unterschiedliche Testanforderungen. Weniger Testkosten durch ML-Techniken wurde bereits von Advantest und seinen Kunden erforscht, wobei signifikante finanzielle Vorteile festgestellt wurden. Zukünftige Arbeiten zielen darauf ab, fortgeschrittene Modelle zu entwickeln, die Ertrag, Qualität und Zuverlässigkeit präzise vorhersagen. Advantest nutzt auch AI und ML in Produkten wie ACS Adaptive Probe Cleaning und ACS EASY, um das Testen von AI-fähigen Chips zu verbessern und Ausbeuteprobleme zu analysieren.

Zusammenfassend lässt sich sagen, dass der Einsatz von KI, ML und Edge Computing die Halbleiterfertigung entscheidend prägen wird, insbesondere für Chiplets und HI in 2,5D/3D-Gehäusen. Beide Techniken ermöglichen eine umfassende Analyse und eine angemessene Reaktion auf Testdaten, was zu mehr Effizienz in der Halbleiterindustrie führt. (heh)

:quality(80)/p7i.vogel.de/wcms/0a/44/0a44149498fa29427072dfaba4be6a67/0116312831.jpeg)

Digitaler Zwilling

Erste Industriesteuerung in den USA zertifiziert

:quality(80)/p7i.vogel.de/wcms/7b/53/7b53dd1e0db5f41dac65d53309b22f60/0116766442.jpeg)

Automatisierte Konformitätsprüfung

High-Speed-Schnittstellen schneller testen

* Ira Leventhal ist Vice President, Applied Research & Technology, Advantest America INC.

* Dr. Matthias Sauer ist Lab Lead Boeblingen & China, Director Applied Research & Venture Team, Advantest Europe GmbH.

Artikelfiles und Artikellinks

(ID:50026896)

:quality(80)/p7i.vogel.de/wcms/02/46/0246a163cd4f770fc4ec4707eed026a3/0118485226.jpeg)

:quality(80)/p7i.vogel.de/wcms/1d/33/1d33974fef7933ea30c16340eebef3c9/0118272751.jpeg)

:quality(80)/p7i.vogel.de/wcms/de/e9/dee92adb2d0ccca12fc131b4b55a4c51/0118262284.jpeg)

:quality(80)/p7i.vogel.de/wcms/95/6b/956b79c5c7020ec2b40ce6e2717941da/0118547893.jpeg)

:quality(80)/p7i.vogel.de/wcms/56/3d/563df7482bac59034c2c1ba6949eabeb/0118519606.jpeg)

:quality(80)/p7i.vogel.de/wcms/04/e7/04e7948f02e1d792f245d19fbb6f84be/0118504854.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/76/0d76806079a5a3d36aacdb006a7aba5a/0118407519.jpeg)

:quality(80)/p7i.vogel.de/wcms/7e/bb/7ebbb9e0afa7f66bd9abed55322eb88e/0118350007.jpeg)

:quality(80)/p7i.vogel.de/wcms/0f/89/0f89b224c4b3bb6fda7cbec9c56d9072/0118533982.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/0d/1a0d73826922a88118e8f6e04799665d/0118425986.jpeg)

:quality(80)/p7i.vogel.de/wcms/72/5f/725fbe6121731518e12f6d0b8d7397cd/0118433936.jpeg)

:quality(80)/p7i.vogel.de/wcms/43/a5/43a5630d2a63fbe82f29e17b71d5dcb3/0118499684.jpeg)

:quality(80)/p7i.vogel.de/wcms/74/47/7447ac45f80368ce7f86b76af1c6da99/0118407224.jpeg)

:quality(80)/p7i.vogel.de/wcms/ce/39/ce39569b6845cb072030fdf6505fb7c5/0118404058.jpeg)

:quality(80)/p7i.vogel.de/wcms/c9/22/c9228b8ec955c03dc075e8875f4cabf8/0117754897.jpeg)

:quality(80)/p7i.vogel.de/wcms/07/6f/076f09c7a697f193091a6e6be846aef1/0117862638.jpeg)

:quality(80)/p7i.vogel.de/wcms/30/51/305138abdaeda721646661bf6ac4fdbd/0117756540.jpeg)

:quality(80)/p7i.vogel.de/wcms/3c/b9/3cb980e98baaaadddf69a5dad4ad20a0/0117334644.jpeg)

:quality(80)/p7i.vogel.de/wcms/31/8c/318c8c9e8d61814564d11967ccc14c04/0118494408.jpeg)

:quality(80)/p7i.vogel.de/wcms/eb/6c/eb6c99643aca684c44f5ad0411d71f3f/0118318941.jpeg)

:quality(80)/p7i.vogel.de/wcms/79/4b/794b7d23361d39306753a0abab662274/0117836261.jpeg)

:quality(80)/p7i.vogel.de/wcms/84/64/846421e1abb64717319a401a350ed9ff/0118471925.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/06/b606e1899c3d19b8ac0bf5cdada67cd8/0118340949.jpeg)

:quality(80)/p7i.vogel.de/wcms/42/a0/42a0d035baeb02bf4467dd19ad99f583/0118352721.jpeg)

:quality(80)/p7i.vogel.de/wcms/36/94/36944586a51513ee0dc4cbb1fa410689/0118252602.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/bc/9cbcc8436fa8e226234cebdd1a101d61/0118377191.jpeg)

:quality(80)/p7i.vogel.de/wcms/38/59/385995468963d81ae3df2bb20ad2f88e/0118499672.jpeg)

:quality(80)/p7i.vogel.de/wcms/70/91/7091aed6e9292abc5451815f9499984b/0118509991.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/59/e15978926ae2637c5cc1cb07fc9428a6/0118508628.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/66/c266c5cfbc51fb7d06557ee079d406bf/0116839110.jpeg)

:quality(80)/p7i.vogel.de/wcms/3a/1a/3a1a267224e51b795ccc6b8df959f18e/0115998041.jpeg)

:quality(80)/p7i.vogel.de/wcms/3d/14/3d1447535880e284712d1daba8d7d466/0115848899.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/119600/119672/65.png)

:fill(fff,0)/p7i.vogel.de/companies/66/1f/661fa8e004810/heitec-logo-2024-1200px-ae.png)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/111200/111228/65.jpg)

:quality(80)/p7i.vogel.de/wcms/d0/c6/d0c6f2ea3d6ef32959565759245a41ee/0117167431.jpeg)

:quality(80)/p7i.vogel.de/wcms/34/4c/344cb149906bdc4d7d3296fbb74967af/0115575996.jpeg)