Probleme in der Chipfertigung Chipevolution in sechs Wellen: Moore’s Law auf dem Prüfstand

Anbieter zum Thema

Bisher hat sich Moore's Law seit 1965 bewahrheitet. Auch wenn das Ende mehrfach prognostiziert wurde. Eine neue Analyse zeigt, dass die Miniaturisierung von ICs durch höhere Transistordichte in sechs Phasen ablief, die durch bahnbrechende Transistor-Entwicklungen geprägt wurden.

Der Transistor gilt als „die Erfindung des 20. Jahrhunderts“. Seit 1948 hat er viele Evolutionsstufen durchlaufen, bei denen die Bauelemente leistungsfähiger, integrierter, komplexer und kleiner wurden. So enthielt 1971 der Intel i4004 17.000 Transistoren/cm2, also einige 1000; 2009 der Intel Yorkfield 390 Mio. Transistoren/cm2 und der AMD Phenom II 290 Mio. Transistoren/cm2, also bereits einige 100 Mio. Transistoren.

Gordon More fasste das bereits 1965 in seinem bekannten Gesetz zusammen, demzufolge die Anzahl der Transistoren in integrierten Schaltkreisen exponentiell ansteigt und sich alle 12 bis 24 Monate verdoppelt. Für 2020 wurde das Ende des Moore’schen Gesetzes prognostiziert. Eingetreten ist das bisher nicht.

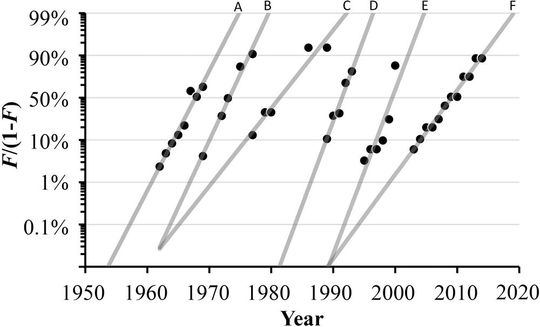

Zwei Analysten von der Rockefeller Universität in New York, David Burg und Jesse H. Asubel, kommen auf Basis von Intel-Daten nun zu einer interessanten Erkenntnis: Die Chip-Entwicklung verläuft seit 1959 in sechs Wellen.

In jeder Welle stieg die Transistordichte im Laufe von etwa sechs Jahren um mindestens das Zehnfache, gefolgt von mindestens drei Jahren mit vernachlässigbaren Wachstumsraten. Miniaturisierungswellen (höhere Transistordichte auf den Chips) hätten die Marktentwicklung möglicherweise ebenso vervielfacht wie wachsende Chipdurchmesser. Das verdeutlicht Bild 1.

Die erste Welle korrespondiert demnach mit der Entwicklung des ersten kommerziellen Planartransistors aus Silizium und der Anpassung der Photolithographietechniken durch Fairchild (Bell Labs) 1954 bzw. 1955 (Linie A).

Den Beginn der zweiten Welle (Linie B) markiert die Entwicklung des Metall-Oxid-Halbleiter-Feldeffekttransistors (MOSFET), der 1964 von General Microelectronics auf den Markt gebracht wurde.

Die von Intel eingeführte Silizium-Gate-Technologie (SGT) markiert den Beginn der dritten Welle. Die Silizium-Gate-Technologie war der Vorläufer für alle nachfolgenden Mikroprozessoren, beginnend mit dem 4004 und dem 8080, die 1971 auf den Markt kamen.

Der 1977 patentierte Kurzkanal MOSFET (HMOS) erhöhte die Transistordichte für den 1978 eingeführten 8086 erheblich. Der 80486, der 1989 auf den Markt kam, enthielt noch wesentlich mehr Transistoren und ermöglichte die Integration komplexer Schaltkreise, wie z. B. einen 8-KB-Cache und einen Gleitkomma-Coprozessor (Linie E).

Die 1982 entwickelte Deep-UV-Lithografie wurde in den 1990er Jahren kommerziell eingesetzt, was laut Burg und Asubel auf die sechste Welle hinweist (Linie F), da alle seit 1998 auf den Markt gebrachten Prozessoren mit dieser Technik hergestellt wurden.

Die wichtigsten Meilensteine in der Transistorevolution sehen die Analysten in der Silizium-Gate-Technologie und der Deep-UV-Lithografie.

Hat das Moore'sche Gesetz doch ausgedient?

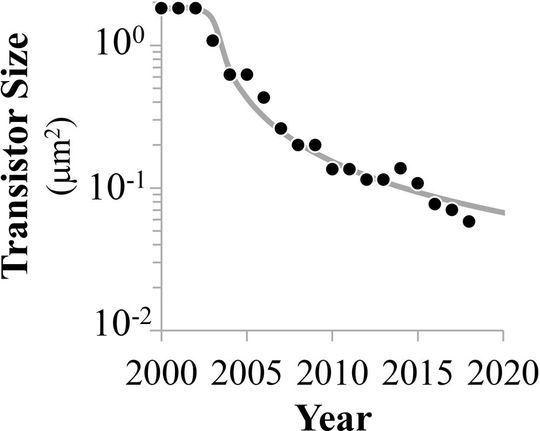

Die Daten seit dem Jahr 2000 zeigen eine deutliche Verlangsamung der Miniaturisierung (Bild 2), die selbst Entwicklungen wie Intels 3D-Tri-Gate-Technik nicht aufhalten konnten.

Burg und Asubel sehen darin auch eine Erklärung für die aktuellen Schwierigkeiten, Fertigungstechniken für 10 nm, 7 nm oder kleinere Prozessknoten in die Massenproduktion zu überführen. (Intel hat 2014 die Angabe von Prozessknoten eingestellt.)

Transistoren: Rückgang der Miniaturisierungsraten

Die Analysten konstatieren, dass trotz bedeutender technischer und wissenschaftlicher Fortschritte im letzten Jahrzehnt wie zum Beispiel „gepanntes“ SiGe, High-k-Metall-Gate-Transistoren, Lithografietechniken mit verbesserter Auflösung und FinFETs ein Rückgang der Miniaturisierungsraten zu verzeichnen war.

Die Entwicklung der Transistordichte in den letzten zehn Jahren entspricht demnach einem linearen Trend, der auf langsame und schrittweise Fortschritte hindeutet, aber auch eine deutliche Abweichung vom Moore'schen Exponentialgesetz darstellt, so die Analysten. Sie spekulieren, dass die Transistordichte tatsächlich eine Sättigung erreichen könnte, allerdings erst nach einem oder möglicherweise zwei weiteren starken Impulsen.

Chipentwicklung: Treiber der nächsten Welle

Wachstumsimpulse kämen u.a. von KI-Entwicklungen, die größere Chips mit schnellem Speicher benötigen. So kündigte Xilinx 2019 die weltweit größten feldprogrammierbaren Gate-Arrays mit 9 Millionen Logikzellen und 35 Milliarden Transistoren an, die höchste Logikdichte auf einem einzigen Baustein, die bisher gebaut wurde. Zielmarkt sind komplexe Algorithmen für maschinelles Lernen, Videoverarbeitung und Sensorintegration.

Startup Cerebras fokussiert ebenfalls auf KI und maschinelles Lernen und hat vergangenes Jahr mit der Wafer-Scale Engine den größten bisher gebauten Chip vorgestellt. Der Chip enthält 1,2 Billionen Transistoren, 400.000 KI-optimierte Kerne (78-mal mehr als die größte GPU) und verfügt über einen 3.000-mal größeren on-Chip-Speicher.

Auch die Infrastruktur für 5G verspricht Potenzial mit enormen Datenvolumina (Zettabyte), um 2030 soll die Yottabyte-Ära erreicht werden.

Transistoren: Aktuelle Entwicklungen

Das Plateau bei der Miniaturisierung von Transistoren deutet auf inhärente technologische Schwierigkeiten hin, meinen Burg und Asubel. Ein Weg sei die Optimierung von Software für parallele Berechnungen, wie sie in Mehrkernprozessoren praktiziert werden. Seit über einem Jahrzehnt werde zudem an der Realisierung von Excimerlaser- und EUV-Messtechnik gearbeitet.

Neue Forschungen liefen zudem auf dem Gebiet der Nanotransistoren und Ein-Atom-Transistoren (2D-Transistoren), während eine weitere Möglichkeit das Quantencomputing sein könnte.

Auch Photonen-Transistoren bilden eine vielversprechende Option. Wie immer es weitergeht – siebte Welle oder das Aus für Silizium und Moores Law – es bleibt spannend.

Originalartikel: „Moore’s Law revisited through Intel chip density“ im Fachmagazin Plos One.

:quality(80)/images.vogel.de/vogelonline/bdb/1934400/1934423/original.jpg)

GHz-2D-Transistoren

Ultraschnelle Transistoren mit Nanodrähten unter Zug

(ID:47998327)

:quality(80)/p7i.vogel.de/wcms/02/46/0246a163cd4f770fc4ec4707eed026a3/0118485226.jpeg)

:quality(80)/p7i.vogel.de/wcms/1d/33/1d33974fef7933ea30c16340eebef3c9/0118272751.jpeg)

:quality(80)/p7i.vogel.de/wcms/de/e9/dee92adb2d0ccca12fc131b4b55a4c51/0118262284.jpeg)

:quality(80)/p7i.vogel.de/wcms/56/3d/563df7482bac59034c2c1ba6949eabeb/0118519606.jpeg)

:quality(80)/p7i.vogel.de/wcms/04/e7/04e7948f02e1d792f245d19fbb6f84be/0118504854.jpeg)

:quality(80)/p7i.vogel.de/wcms/03/c5/03c5925ec95a2630b71e941343a128c5/0118433867.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/76/0d76806079a5a3d36aacdb006a7aba5a/0118407519.jpeg)

:quality(80)/p7i.vogel.de/wcms/7e/bb/7ebbb9e0afa7f66bd9abed55322eb88e/0118350007.jpeg)

:quality(80)/p7i.vogel.de/wcms/0f/89/0f89b224c4b3bb6fda7cbec9c56d9072/0118533982.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/0d/1a0d73826922a88118e8f6e04799665d/0118425986.jpeg)

:quality(80)/p7i.vogel.de/wcms/72/5f/725fbe6121731518e12f6d0b8d7397cd/0118433936.jpeg)

:quality(80)/p7i.vogel.de/wcms/43/a5/43a5630d2a63fbe82f29e17b71d5dcb3/0118499684.jpeg)

:quality(80)/p7i.vogel.de/wcms/74/47/7447ac45f80368ce7f86b76af1c6da99/0118407224.jpeg)

:quality(80)/p7i.vogel.de/wcms/ce/39/ce39569b6845cb072030fdf6505fb7c5/0118404058.jpeg)

:quality(80)/p7i.vogel.de/wcms/c9/22/c9228b8ec955c03dc075e8875f4cabf8/0117754897.jpeg)

:quality(80)/p7i.vogel.de/wcms/07/6f/076f09c7a697f193091a6e6be846aef1/0117862638.jpeg)

:quality(80)/p7i.vogel.de/wcms/30/51/305138abdaeda721646661bf6ac4fdbd/0117756540.jpeg)

:quality(80)/p7i.vogel.de/wcms/3c/b9/3cb980e98baaaadddf69a5dad4ad20a0/0117334644.jpeg)

:quality(80)/p7i.vogel.de/wcms/31/8c/318c8c9e8d61814564d11967ccc14c04/0118494408.jpeg)

:quality(80)/p7i.vogel.de/wcms/eb/6c/eb6c99643aca684c44f5ad0411d71f3f/0118318941.jpeg)

:quality(80)/p7i.vogel.de/wcms/79/4b/794b7d23361d39306753a0abab662274/0117836261.jpeg)

:quality(80)/p7i.vogel.de/wcms/84/64/846421e1abb64717319a401a350ed9ff/0118471925.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/06/b606e1899c3d19b8ac0bf5cdada67cd8/0118340949.jpeg)

:quality(80)/p7i.vogel.de/wcms/42/a0/42a0d035baeb02bf4467dd19ad99f583/0118352721.jpeg)

:quality(80)/p7i.vogel.de/wcms/36/94/36944586a51513ee0dc4cbb1fa410689/0118252602.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/bc/9cbcc8436fa8e226234cebdd1a101d61/0118377191.jpeg)

:quality(80)/p7i.vogel.de/wcms/70/91/7091aed6e9292abc5451815f9499984b/0118509991.jpeg)

:quality(80)/p7i.vogel.de/wcms/08/de/08de3cefb97266232f475bb011d9b0c6/0118162151.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/59/e15978926ae2637c5cc1cb07fc9428a6/0118508628.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/66/c266c5cfbc51fb7d06557ee079d406bf/0116839110.jpeg)

:quality(80)/p7i.vogel.de/wcms/3a/1a/3a1a267224e51b795ccc6b8df959f18e/0115998041.jpeg)

:quality(80)/p7i.vogel.de/wcms/3d/14/3d1447535880e284712d1daba8d7d466/0115848899.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/10800/10894/65.jpg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/9600/9682/65.jpg)

:fill(fff,0)/p7i.vogel.de/companies/62/6f/626f9753a3e5a/a-category-images-970x300-logo.jpeg)

:quality(80)/p7i.vogel.de/wcms/ce/62/ce629ae8739dc12583e0a7286bb653c8/0116534698.jpeg)

:quality(80)/p7i.vogel.de/wcms/a2/24/a2249bc111c69b9af5404fc356834e9b/0118129754.jpeg)