Halbleiterintegration Kommentar: Warum das Mooresche Gesetz nicht tot ist

Anbieter zum Thema

Der Tech-Journalist Christopher Mims plädierte im Wall Street Journal dafür, das Huangsche Gesetz einzuführen, da das Mooresche Gesetz obsolet sei. Doch ist die Halbleitertechnik wirklich in der atomaren Sackgasse angelangt oder gibt es noch „Luft nach oben“?

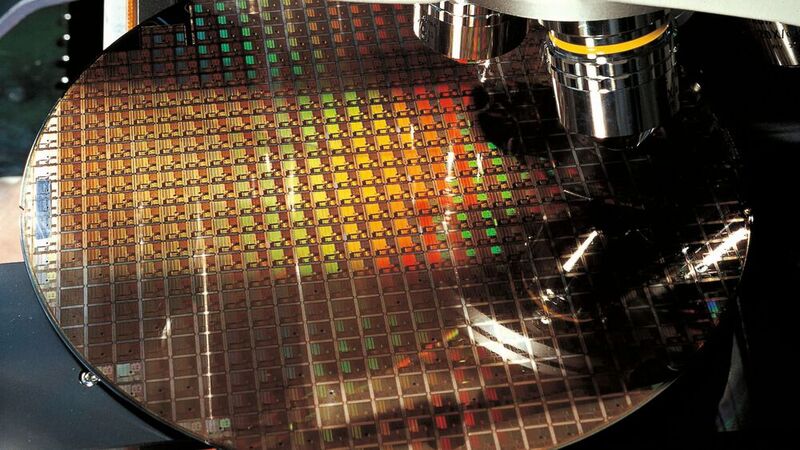

Ein halbes Jahrhundert schien die Beobachtung Gordon Moores, dass sich die Integrationsdichte, also die Anzahl von Transistoren pro Flächeneinheit, ungefähr alle zwei Jahre verdoppelt, ziemlich gut zuzutreffen. Nun glauben einige, dass das Mooresche Gesetz ein Auslaufmodell ist, weil man den Transistor nach 2029 nicht weiter verkleinern kann. Folgen soll das Huangsche Gesetz, wonach sich die Leistung von Computerchips, die KI-Algorithmen treiben, alle zwei Jahre verdoppelt, unabhängig vom technischen Aufbau.

Ist die Entwicklung von Halbleiter-Bausteinen tatsächlich in der atomaren Sackgasse angelangt und muss Software oder Quantencomputing Platz machen? Oder verdeckt der Fokus auf die (nicht miteinander vergleichbaren) „Nodes“ die Tatsache, dass es andere Wege gibt, die Halbleitertechnik voranzutreiben?

Gordon Moore, Forschungsdirektor von Fairchild und Mitbegründer Intels, war ein exzellenter Beobachter, Analyst und Visionär. Seine Prognose zur Halbleitertechnik wurde, weil sie so genau zutraf, in den Rang eines Gesetzes erhoben. Nicht von ihm, der eigentlich immer nur die Wirtschaftlichkeit im Hinterkopf hatte.

Den Zusammenhang zwischen kleiner werdenden Transistoren, höherer Taktfrequenz und dem Stromverbrauch der ICs stellte später Robert Dennard her. Und auf Fred Pollack geht zurück, dass die Verdopplung der Komplexität eines Mikroprozessors zu einer Steigerung bei der Verarbeitungsleistung um den Faktor Wurzel 2 führt. Oft werden diese drei wichtigen Aussagen durchmischt und unter dem Begriff Mooresches Gesetz subsummiert.

Das bedeutungslose Maß der Dinge – die „Nodes“

Damit die rasanten Entwicklungen der Chiphersteller vergleichbar wurden, führte man als Maß für die Integrationsdichte die „Nodes“ in nm ein. Mit aktuell 5 nm lateral (Samsung, TSMC) ist die Lithografie an ihrer technischen Grenze und die Strukturen im atomaren Maßstab angelangt.

Trotzdem gehen die Branchenführer davon aus, dass sie innerhalb eines Jahrzehnts am 1-nm-Knoten arbeiten werden. (1 nm entspricht etwa der Breite von fünf Siliziumatomen.) Es ist weniger die Physik, die Grenzen setzt, sondern vielmehr die mangelnde Fähigkeit, große Stückzahlen mit hoher Präzision aufgrund quantenmechanischer Effekte zu produzieren.

Und was kommt danach? Denken Sie jetzt bitte dreidimensional weiter an das Stapeln von Silizium-Transistoren. Bis der „monolithische 3D-IC“ dem Labormaßstab entwachsen ist, dürfte es gar nicht mehr lange dauern. Das belgische Forschungsinstitut Imec, das französische CEA-Leti und Intel arbeiten an Verfahren, mit denen die beiden Silizium-Transistortypen in CMOS-Logik – NMOS und PMOS – übereinander gestapelt werden können.

Noch früher könnten Transistoren aus Schichten von Kohlenstoff-Nanoröhrchen in 3D umgesetzt werden. Exemplarisch seien hier die weit fortgeschrittenen Arbeiten des Teams um MIT-Professor Max Shulaker genannt. Andere Forscher arbeiten an Logik- oder Speicherbausteinen, die innerhalb der Metallisierung aufgebaut werden. Dazu gehören auch mikromechanische Relais und Transistoren aus atomdünnen Halbleitern wie Wolframdisulfid. Für mich ist da kein Ende von Moore’s Law in Sicht.

Neue Parameter für die Integrationsdichte: GMT und LMI

Anders sieht es bei den „Nodes“ aus. Paolo Gargini, IEEE Fellow und Intel-Veteran, hat im April 2020 empfohlen, dass „die Industrie zur Realität zurückkehren solle“, indem sie ein sinnvolles Maß einführt, das die Transistordichte beschreibt. Das wären beispielsweise der Abstand der kontaktierten Gates (G), der Metallabstand (M) und die Anzahl der gestapelten Bausteine auf dem Chip (T). „Diese drei Parameter GMT sind alles, was man wissen muss, um die Transistordichte zu beurteilen", erklärt Gargini.

Ein anderer Ansatz (LMI) beschreibt die Dichte von Logik (Transistoren pro mm2), System-Hauptspeicher (Speicherzellen pro mm2) und die Anzahl der Verbindungen zwischen Logik und Hauptspeicher. Wenn es mehrere Schichten von Transistoren oder einen 3D-Stapel von Bausteinen gibt, zählt das gesamte Volumen über diesem mm2.

Mit Blick auf die genannten Aspekte erwartet Intel, dass die aus dem Mooreschen Gesetz ableitbaren ökonomischen Vorteile weiterhin Gültigkeit behalten, auch wenn sich die Bauelemente von denen unterscheiden, die es gab, als Moore seine ursprüngliche Beobachtung machte.

Es lebe das Mooresche Gesetz 4.0

Entwicklungen in der Halbleitertechnik werden künftig durch 3D, neue Werkstoffe und neue Formen der Integration wie die Zusammenführung unterschiedlicher Fähigkeiten auf einem einzigen Chip und die Integration von Nicht-Standard-Komponenten definiert werden. Das Mooresche Gesetz, wie wir es kennen, wandelt sich zum Mooreschen Gesetz 4.0 oder anders bekannt zu More than Moore.

Rechenaufgaben künstlicher Intelligenz – das maschinelle Lernen (intensive Rechenoperationen, große Datenmengen, hoher Energieverbrauch) und KI-Interferenzierung (Schnelligkeit und geringe Latenzzeiten) – sind eher auf Systemebene, wo der Speicher entscheidend ist, anzusiedeln. Hier darf man auf die Fortschritte bei Architektur, Verbindungen, Speichertechnik, Algorithmen etc. gespannt sein. Nvidia-Chef Jensen Huang wird sicher maßgeblich zu diesen Entwicklungen beitragen. Ob seine eingangs genannte Prognose – wie von ihm erhofft – ein eigenes Gesetz wert ist, wird die Zukunft zeigen.

:quality(80)/p7i.vogel.de/wcms/f2/80/f28057b3185597af34bc736356bc8a3e/91829770.jpeg)

Kommentar: Das „Moore‘sche Gesetz“ ist out – gilt jetzt „Huangs Gesetz“?

(ID:46896654)

:quality(80)/p7i.vogel.de/wcms/02/46/0246a163cd4f770fc4ec4707eed026a3/0118485226.jpeg)

:quality(80)/p7i.vogel.de/wcms/1d/33/1d33974fef7933ea30c16340eebef3c9/0118272751.jpeg)

:quality(80)/p7i.vogel.de/wcms/de/e9/dee92adb2d0ccca12fc131b4b55a4c51/0118262284.jpeg)

:quality(80)/p7i.vogel.de/wcms/56/3d/563df7482bac59034c2c1ba6949eabeb/0118519606.jpeg)

:quality(80)/p7i.vogel.de/wcms/04/e7/04e7948f02e1d792f245d19fbb6f84be/0118504854.jpeg)

:quality(80)/p7i.vogel.de/wcms/03/c5/03c5925ec95a2630b71e941343a128c5/0118433867.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/76/0d76806079a5a3d36aacdb006a7aba5a/0118407519.jpeg)

:quality(80)/p7i.vogel.de/wcms/7e/bb/7ebbb9e0afa7f66bd9abed55322eb88e/0118350007.jpeg)

:quality(80)/p7i.vogel.de/wcms/0f/89/0f89b224c4b3bb6fda7cbec9c56d9072/0118533982.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/0d/1a0d73826922a88118e8f6e04799665d/0118425986.jpeg)

:quality(80)/p7i.vogel.de/wcms/72/5f/725fbe6121731518e12f6d0b8d7397cd/0118433936.jpeg)

:quality(80)/p7i.vogel.de/wcms/43/a5/43a5630d2a63fbe82f29e17b71d5dcb3/0118499684.jpeg)

:quality(80)/p7i.vogel.de/wcms/74/47/7447ac45f80368ce7f86b76af1c6da99/0118407224.jpeg)

:quality(80)/p7i.vogel.de/wcms/ce/39/ce39569b6845cb072030fdf6505fb7c5/0118404058.jpeg)

:quality(80)/p7i.vogel.de/wcms/c9/22/c9228b8ec955c03dc075e8875f4cabf8/0117754897.jpeg)

:quality(80)/p7i.vogel.de/wcms/07/6f/076f09c7a697f193091a6e6be846aef1/0117862638.jpeg)

:quality(80)/p7i.vogel.de/wcms/30/51/305138abdaeda721646661bf6ac4fdbd/0117756540.jpeg)

:quality(80)/p7i.vogel.de/wcms/3c/b9/3cb980e98baaaadddf69a5dad4ad20a0/0117334644.jpeg)

:quality(80)/p7i.vogel.de/wcms/31/8c/318c8c9e8d61814564d11967ccc14c04/0118494408.jpeg)

:quality(80)/p7i.vogel.de/wcms/eb/6c/eb6c99643aca684c44f5ad0411d71f3f/0118318941.jpeg)

:quality(80)/p7i.vogel.de/wcms/79/4b/794b7d23361d39306753a0abab662274/0117836261.jpeg)

:quality(80)/p7i.vogel.de/wcms/84/64/846421e1abb64717319a401a350ed9ff/0118471925.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/06/b606e1899c3d19b8ac0bf5cdada67cd8/0118340949.jpeg)

:quality(80)/p7i.vogel.de/wcms/42/a0/42a0d035baeb02bf4467dd19ad99f583/0118352721.jpeg)

:quality(80)/p7i.vogel.de/wcms/36/94/36944586a51513ee0dc4cbb1fa410689/0118252602.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/bc/9cbcc8436fa8e226234cebdd1a101d61/0118377191.jpeg)

:quality(80)/p7i.vogel.de/wcms/70/91/7091aed6e9292abc5451815f9499984b/0118509991.jpeg)

:quality(80)/p7i.vogel.de/wcms/08/de/08de3cefb97266232f475bb011d9b0c6/0118162151.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/59/e15978926ae2637c5cc1cb07fc9428a6/0118508628.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/66/c266c5cfbc51fb7d06557ee079d406bf/0116839110.jpeg)

:quality(80)/p7i.vogel.de/wcms/3a/1a/3a1a267224e51b795ccc6b8df959f18e/0115998041.jpeg)

:quality(80)/p7i.vogel.de/wcms/3d/14/3d1447535880e284712d1daba8d7d466/0115848899.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/63/88/63887b860cf66/me-logo-400px.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/114400/114404/65.jpg)

:fill(fff,0)/p7i.vogel.de/companies/62/5e/625ea073a6efe/eepd-just-embedded-4zu1.jpeg)

:quality(80)/p7i.vogel.de/wcms/de/89/de8956f8a3c454ac651a8ffa3303c89f/0117868030.jpeg)

:quality(80)/p7i.vogel.de/wcms/ce/62/ce629ae8739dc12583e0a7286bb653c8/0116534698.jpeg)