Weniger ESD-induzierte Ausfälle Moderne CMOS-ICs mit eingebautem Elektrostatikschutz

Anbieter zum Thema

Integrierte Schaltkreise sind hochempfindlich gegenüber statischen Entladungen. Bereits der Aufbau von gestapelten 3D-Chips per Advanced-Packaging-Verfahren ist überaus heikel. Imec will das Problem über die funktionale Rückseite der Chips lösen. Die Forschungsergebnisse für den ESD-Schutz von Dünnschicht-CMOS-Technologien sind ermutigend.

Wohl jeder hat schon einmal elektrostatische Entladungen (ESD) im Alltag erlebt. Beispielsweise wenn Sie über einen Teppich gehen und dann einen metallischen Türknauf berühren. In diesem Fall fließen Ladungen mit einigen tausend Volt (V) und mehr, die sich während des Gehens im menschlichen Körper angesammelt haben, blitzschnell über die Türklinke ab.

Während der Mensch gegenüber Entladungen von bis zu 3000 V recht unempfindlich ist, können elektronische Geräte bereits durch Entladungen von nur 3 V beschädigt werden. Alle elektronischen Produkte und Technologien – sei es auf Komponenten- oder Systemebene – können von ESD-Ereignissen betroffen sein. Diese können zu jedem Zeitpunkt während der Herstellung und Montage sowie während des Transports und der Verwendung des Produkts auftreten. Bei der Montage kann zum Beispiel ein Chip beschädigt werden, wenn er auf einer Leiterplatte montiert oder mit einer Pinzette mit unterschiedlichen elektrostatischen Potentialen angefasst wird. Bei der Verwendung kann es zu Schäden kommen, wenn Menschen die Ein- und Ausgangspins eines IC-Bausteins berühren.

ESD-induzierte Ausfälle in elektronischen Produkten sind seit langem ein Problem

Charakteristisch für ESD-Ereignisse ist ihre kurze Dauer, ein Merkmal, das sie von vergleichbaren, aber länger andauernden elektrischen Überlastungsereignissen (EOS) unterscheidet. Die ESD-Entladung erfolgt in einem sehr kurzen Zeitrahmen (etwa 1 ns oder in der Größenordnung von 200 ns, je nach Art des ESD-Ereignisses), mit Anstiegszeiten von 200 ps bis 10 ns. In dieser kurzen Zeitspanne fließen überschüssige Ströme in der Größenordnung von 0,1 – 10 A durch den IC und das Gehäuse, wobei eine Leistung von 10 – 100 W abgeleitet wird. Der Chip selbst kann beschädigt werden, z.B. durch Durchbrennen der Metallverbindungen, Bruch des Gate-Oxids oder Zusammenbruch des Übergangs.

Die Auswirkungen von ESD auf elektronische Geräte können gar nicht hoch genug eingeschätzt werden. Seitdem die Technologieknoten in den Submikronbereich vorgedrungen sind, hat sich ESD zur häufigsten Fehlerursache entwickelt. Industrielle Statistiken deuten darauf hin, dass heute fast 40 Prozent der IC-Ausfälle auf EOS/ESD-Ereignisse zurückzuführen sind, was der Industrie jährlich Verluste in Milliardenhöhe beschert. Es ist daher nicht verwunderlich, dass die Halbleiterindustrie stark darauf setzt, Anzahl, Ausmaß und Folgen von ESD-Ereignissen zu reduzieren.

Maßnahmen zum Schutz von ICs: Prävention und Schutz

Es werden große Anstrengungen unternommen, um ESD-Ereignisse in der Umgebung zu verhindern – bei der Herstellung, der Montage und dem Transport von ICs. Die Herstellung und Montage erfolgt in streng ESD-kontrollierten Umgebungen, in denen geeignete Materialien verwendet werden und Personal und Geräte ordnungsgemäß geerdet sind. Diese antistatischen Maßnahmen werden kontinuierlich verbessert, um sicherzustellen, dass sich während der kritischen Schritte so wenig statische Ladungen wie nur möglich aufbauen und entladen.

Da sich durch die Prävention nicht alle ESD-Ereignisse ausschließen lassen, wird sie durch einen zusätzlichen On- und Off-Chip-Schutzschaltkreis ergänzt. Chipinterne ESD-Schutzschaltungen spielen eine wichtige Rolle bei der Abschirmung der Stromversorgungsleitungen und der Masse des Chips sowie der Eingangs- und Ausgangsschnittstellen (I/O), die mit der Außenwelt kommunizieren. Wenn ein ESD-Ereignis auf den Chip trifft, sorgen die ESD-Schaltungen für einen sicheren, niederohmigen Entladungspfad zur Masse und begrenzen gleichzeitig die Spannung auf ein sicheres Niveau.

Robustheit gegenüber ESD-Ereignissen qualifizieren

Um die Leistung der ESD-Schutzvorrichtungen zu messen und die Robustheit des Chips gegenüber ESD-Ereignissen zu qualifizieren, stützt sich die Halbleiterindustrie auf zwei Standards, die für die häufigsten ESD-Ereignisse repräsentativ sind. Der Standard Human Body Model (HBM, ca. 200 ns Dauer), der ursprünglich die Entladung von einem Menschen auf das Gerät darstellte, umfasst heute auch Entladungen von anderen externen Objekten innerhalb von Fertigungs- und Montagelinien. Das Modell des geladenen Geräts (CDM, ca. 1 ns Dauer) hingegen emuliert, was passiert, wenn der Chip selbst aufgeladen wird und sich in die Umgebung entlädt. Die I-U-Charakteristiken, die durch Anwendung von Transmission Line Pulse (TLP)-Stress und Very Fast TLP (VF-TLP)-Stress gemessen werden, entsprechen der Leistung der Bauelemente mit HBM bzw. CDM.

Heutzutage verlangt die Halbleiterindustrie in der Regel 250 V CDM als Spezifikation für die modernsten Technologien, die in Hochleistungscomputeranwendungen eingesetzt werden. Bei HBM hängt die Spezifikation von der Funktionalität der I/O-Pins ab. Für die generellen I/O-Pins sowie für die Stromversorgungs- und Erdungsleitungen können die Spezifikationen 500 V HBM und mehr erreichen, während für die High-Speed I/O-Pins etwa 100 V angenommen werden. Das Hinzufügen von ESD-Schutzschaltungen erhöht jedoch die Kosten des elektronischen Systems, so dass sich Unternehmen manchmal für niedrigere Zielwerte entscheiden. Die Spezifikationen unterscheiden sich auch je nach Anwendungsgebiet. In der Automobilindustrie beispielsweise gelten eigene Standards, und es wird eine ESD-Robustheit gegen einige tausend Volt gefordert, um die Sicherheit der Menschen zu gewährleisten.

Unterschiedliche ESD-Schutzvorrichtungen verfügbar

Es gibt verschiedene Arten von ESD-Schutzvorrichtungen. Die richtige Wahl hängt von der Art der Schaltung ab, die geschützt werden muss. ESD-Dioden, sowohl STI-Dioden (shallow trench isolation) als auch Gatterdioden, sind die am häufigsten verwendeten. Sie sind strukturell einfach aufgebaut und gelten in Durchlassrichtung als eines der effektivsten Schutzelemente mit einer niedrigen Einschaltspannung, einem geringen Durchlasswiderstand und der Fähigkeit, hohe ESD-Ströme zu verarbeiten. Sie werden z.B. zum Schutz der Eingangspins des ICs verwendet. ESD-Dioden werden oft mit Stromschienen-Klemmen zwischen Stromversorgung und Masse kombiniert, um niedrige Spannungspegel zu gewährleisten. Neben Dioden sind auch Grounded-Gate-NMOS (GGNMOS) in ESD-Designs beliebt. GGNMOS sind MOSFETs im Aus-Zustand, die den ESD-Strom über einen parasitären bipolaren Leitungsmechanismus ableiten.

Ob in Form von Dioden oder kanalbasierter MOSFETs: Alle ESD-Bauteile haben transistorähnliche Strukturen, die während der Front-End-of-Line (FEOL) Verarbeitung des Chips hergestellt werden. Sie nutzen in der Regel dieselben CMOS-Technologien, die für die Herstellung der Kerntransistoren des Chips verwendet werden. Um die überschüssigen Ströme effizient zur Masse abzuleiten und die Wärme abzuführen, nutzen die meisten ESD-Schutzschaltungen das dicke Si-Substrat, das sich auf der Rückseite des Chips befindet.

Neue Technologien stellen eine Herausforderung für ESD-Schutzkonzepte dar

Wenn neue Technologien in die Roadmap der Halbleitertechnologie aufgenommen werden, kann dies auch neue ESD-Schwachstellen mit sich bringen, die der Halbleiterindustrie Probleme bereiten. Um kommende Anforderungen besser zu beschreiben und neue Standards zu definieren, arbeitet die Chipindustrie daher eng mit der EOS/ESD Association zusammen, an der imec aktiv beteiligt ist.

Mit der Skalierung von CMOS schrumpft der Raum für die Implementierung von ESD-Schutzschaltungen entsprechend. Außerdem kann sich die Skalierung der Abmessungen von Logiktransistoren auf die Leistung von ESD-Schutzvorrichtungen auswirken, die teilweise in derselben Technologie hergestellt werden. Ein ähnliches Problem ergibt sich, wenn neue Transistorarchitekturen auf den Plan treten. Denken Sie nur an den historischen Wechsel von planaren MOSFETs zu FinFET-Bauteilen, die Einführung von Gate-Allaround-FETs (GAA) in den neuesten logischen Technologieknoten und den geplanten Übergang zu komplementären FETs (CFET). Bei monolithischen SOCs hat sich bereits gezeigt, dass sich solche Umstellungen auf die Schutzfunktionen der ESD-Bauteile auswirken [1].

3D-Stacking: Unterscheidung zwischen internen und externen E/A

Zudem verlagern sich die Systemanwendungen zunehmend auf 3D-Stacking-Technologien, ein Trend, der dank des enormen Potenzials der 2,5D- und 3D-Chiplet-Technologien boomt. Aus der ESD-Perspektive unterscheidet man zwischen den externen E/A-Schnittstellen, die mit der Außenwelt kommunizieren, und den internen E/As, die zwischen den Dies oder gestapelten Modulen kommunizieren. Bei den externen E/A ändert sich eigentlich nichts, da diese Schaltkreise nach wie vor elektrostatisch von und zu externen Objekten oder Menschen entladen werden können. Vergleichbare HBM- und CDM-Standards, wie sie für monolithische Chips definiert wurden, bleiben daher gültig.

Für die internen E/A-Schnittstellen gelten jedoch andere Standards. Sobald die externen E/A-Anschlüsse abgeschirmt sind, besteht das Hauptrisiko für eine Beschädigung der internen Verbindungen während des Stapelns und der Montage. Schäden können beispielsweise entstehen, wenn ein elektrostatisch aufgeladener Chip auf einem geerdeten 2,5D-Interposer integriert wird. Bei den internen E/As in 3D-Technologien verlagert sich der Schwerpunkt daher auf eine verstärkte Umfeldkontrolle, um solche Entladungen zu verhindern. Letztendlich besteht das Ziel darin, die Notwendigkeit von On-Chip-ESD-Schaltungen zum Schutz der internen Schnittstellen in 3D-Designs zu beseitigen.

Schließlich werden in der Ära der Design-Technologie-Ko-Optimierung (DTCO) und der System-Technologie-Ko-Optimierung (STCO) neue Skalierungsverstärker (z.B. Backside Power Delivery Networks, BSPDNs) und fortschrittliche 3D-Integrationstechnologien (z.B. Wafer-to-Wafer Hybrid Bonding) zunehmend eingesetzt, um wichtige Engpässe bei der Systemskalierung zu beseitigen. Typisch für diese Technologien ist die Ausdünnung der Si-Substrate auf wenige hundert Nanometer, um Through-Si-Via (TSV)-Verbindungen mit realisierbaren Querschnittsverhältnissen zu ermöglichen. Dies bereitet Probleme, da die meisten konventionellen ESD-Schutzschaltungen stark auf verhältnismäßig dicke Si-Substrate angewiesen sind, um Wärme effizient abführen und sich entladen zu können.

Verdünnung des Si-Substrats verschlechtert ESD-Eigenschaften

Imec hat durch Messungen und Simulationen die Auswirkungen einer extremen Verdünnung des Si-Substrats (von 700 µm auf 300 nm) auf die Leistung verschiedener ESD-Schutzvorrichtungen untersucht, die in FinFET-Technologie hergestellt werden. Dazu gehören STI- und Gatterdioden, Off-State-MOSFETs (genauer gesagt GGNMOS) und On-State-MOSFETs (genauer gesagt Power-Rail-Clamps). Die Leistung der verschiedenen Bauelemente wird hauptsächlich durch ihren Ausfallstrom (It2, die Stromschwelle für eine Beschädigung) widergespiegelt, eine Metrik, die aus TLP- und VF-TLP-I-V-Kurven abgeleitet wird. Das Team untersuchte auch die Auswirkungen der Substratverdünnung auf die Wärmeabführung, indem es die Temperaturen des Gitters simulierte. Diese Ergebnisse wurden auf dem IEEE International Electron Devices Meeting 2023 (IEDM 2023) vorgestellt [2].

Im Allgemeinen zeigen ESD-Schutzvorrichtungen mit dünnen Si-Substraten eine geringere ESD-Robustheit aufgrund einer weniger effizienten Wärmeableitung. Bauelemente mit extrem dünnem Substrat zeigen eine Senkung des Ausfallstroms um 20 – 40 Prozent im Vergleich zu dickeren Varianten. Bei STI-Dioden beispielsweise kann sich die 100 ns TLP It2 um ~36 Prozent verschlechtern, wenn das Substrat von 700 µm auf 300 nm verdünnt wird. In Simulationen wird eine ~2-fach höhere Stromdichte über das 300 nm Si-Substrat im Vergleich zur dicken STI-Diode beobachtet. Es wird eine geringere Degradation (~20 Prozent) von VF-TLP It2 gemessen, da es eine kleinere thermische Diffusionslänge als 100 ns TLP hat.

Wie erwartet, sind die Stromschienenklemmen am wenigsten von der Substratverdünnung betroffen. Diese Bauelemente, die auf On-State-MOSFETs beruhen, leiten den ESD-Strom durch eine Kanalleitung ab, während die anderen Bauelemente bei der Entladung stärker auf das Substrat angewiesen sind.

Funktionale Chiprückseite zur Lösung des Wärmeproblems nutzen

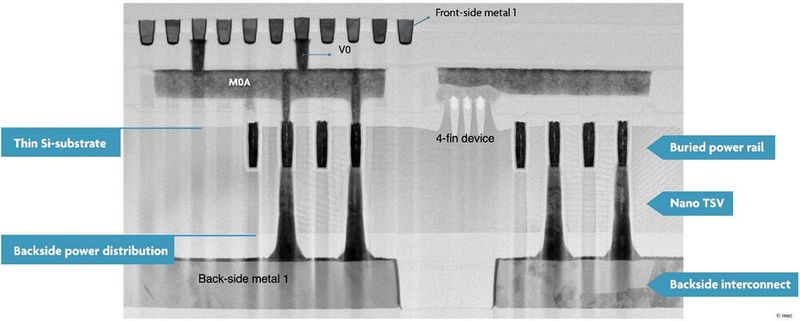

Eine der Technologien, die eine extreme Substratverdünnung erfordern, sind rückseitige Stromversorgungsnetzwerke (BSPDNs). Bei BSPDNs erfolgt die Stromversorgung über die Rückseite des Wafers, so dass das Stromversorgungsnetz von dem Signal- und Taktversorgungsnetz auf der Vorderseite entkoppelt ist. In einer speziellen Implementierung eines BSPDN, die ebenfalls in Bild 3 zu sehen ist, wird der Strom von der Rückseite zu den FinFETs auf der Vorderseite über Nano-TSVs geleitet, die auf einer vergrabenen Stromschiene (BPR) landen. Auf der VLSI 2023 untersuchte Imec die Auswirkungen dieses neuen Routing-Stils mit doppelseitiger Konnektivität der FinFETs auf ESD-Schutzvorrichtungen und stellte Richtlinien für einen besseren Layout-Stil vor [3].

Imec hatte bereits früher vorgeschlagen, das Konzept des BSPDN zu erweitern und andere Bauelemente oder Funktionalitäten auf die Rückseite zu verlagern – ein Ansatz, der als aktive funktionale Rückseitentechnologie bezeichnet wird. Bei der Implementierung auf der Rückseite können die ausgewählten Bauelemente über verschiedene Routing-Schemata verbunden werden, einschließlich der doppelseitigen Konnektivität. Dies bietet auch Möglichkeiten für ESD-Schutzvorrichtungen.

Zu den Vorschlägen zählen vertikale ESD-Dioden, die mit der aktiven funktionalen Rückseitentechnologie hergestellt werden. Der Prozess basiert auf der Technologie von Imec zur Realisierung von extrem dünnem Si und doppelseitiger Konnektivität mit BSPDNs [4]. Zusätzliche Prozessschritte wurden eingefügt, um vertikale Diodenstrukturen zu realisieren, die es ermöglichen, den Anodenanschluss von der Vorderseite auf die Rückseite zu verlegen. Wie auf der VLSI 2022 gezeigt wurde, konnten die vertikalen ESD-Dioden die Layoutfläche im Vergleich zu ESD-Dioden mit nur vorderseitiger Konnektivität um 67 Prozent reduzieren [5]. Außerdem haben die Forscher experimentell eine erhöhte ESD-Robustheit dank der verbesserten Stromhomogenität beobachtet.

Auf der IEDM 2023 präsentierten die Imec-Forscher die erste Studie über das thermische Verhalten dieser vertikalen ESD-Dioden und weiteten ihre Forschung auf andere Arten von ESD-Bauteilen aus [2]. Sie untersuchten, ob die Kontakte auf der Rückseite und die Metallisierungsschichten auf der Rückseite die Wärme effizienter abführen, als wenn nur eine Metallisierung auf der Vorderseite verwendet wird. Simulationen bestätigten, dass diese Merkmale tatsächlich die Hot Spots in verschiedenen ESD-Bauteilen verringern können. Sie könnten auch die elektrischen Eigenschaften der ESD-Bauteile beeinflussen. Aber insgesamt machen diese Ergebnisse ESD-Bauteile mit aktiven Rückseitenkontakten und Metallisierung zu vielversprechenden Kandidaten für fortschrittliche Technologien, die auf eine extreme Verdünnung des Si-Substrats angewiesen sind.

Fazit

Jede neue Technologie, die die Roadmap der Halbleitertechnologie ergänzt, kann Herausforderungen und Chancen für ESD-Schutzvorrichtungen mit sich bringen. Der Schwerpunkt dieses Artikels lag auf den Auswirkungen der Verdünnung des Si-Substrats, einer Grundlagentechnologie für BSPDN und fortschrittliche 3D-Integrationstechnologien. Die Autoren zogen zwei wichtige Schlussfolgerungen. Erstens verschlechtern verdünnte Si-Substrate die ESD-Robustheit von Dioden- und MOSFET-basierten ESD-Bauteilen aufgrund einer schlechteren Wärmeabführung. Zweitens bietet die aktive funktionale Rückseite mit doppelseitiger Konnektivität Möglichkeiten für die Entwicklung robusterer ESD-Schutzvorrichtungen. (me)

:quality(80)/p7i.vogel.de/wcms/8f/fc/8ffc4b738b918dc451566ece80092e78/0112749527.jpeg)

Interview: Chipfertigung mit High-NA-EUV

„Die komplexen Probleme der Chipfertigung lassen sich nur gemeinsam lösen“

:quality(80)/p7i.vogel.de/wcms/af/2b/af2b595760828a88ef28eb9b99320bda/0116419385.jpeg)

Präziseste Maschine zur Chipfertigung

High-NA-EUVL: Riesige Technik für winzige Transistoren

:quality(80)/p7i.vogel.de/wcms/5c/2b/5c2b0a75226e0b2f6873c9f440787944/0115969995.jpeg)

Perowskit-LED

Tausend Mal heller als moderne OLEDs

Autoren

Wen-Chieh Chen erhielt 2016 bzw. 2018 den B.S. und M.Sc. an der National Chiao-Tung University, Hsinchu, Taiwan. Sie promoviert derzeit an der KU Leuven, Leuven, Belgien. Seit 2019 ist sie Doktorandin im ESD-Team von imec. Ihre Forschungsinteressen umfassen Mixed-Voltage-I/O-Schaltungsdesign und ESD-Bauteilcharakterisierung in fortgeschrittenen Sub-5nm-Technologien und DTCO/STCO.

Marko Simicic erwarb 2010 bzw. 2012 den Bachelor- und Master-Abschluss in Elektrotechnik und Informationstechnologie an der Universität Zagreb, Kroatien. Im Jahr 2018 wurde er an der Fakultät für Elektrotechnik ESAT, KU Leuven, Belgien, promoviert. Seit 2017 ist er Mitglied des ESD-Teams bei imec, Belgien. Seit 2022 ist er ein zertifizierter ESD-Kontrollprogramm-Manager. Er ist Autor oder Co-Autor von mehr als 35 Artikeln in internationalen Fachzeitschriften und Konferenzberichten. Sein derzeitiges Forschungsgebiet ist recht breit gefächert und umfasst ESD-Bauteil- und Schaltungsdesign in fortschrittlichen Halbleiter- und 3D/2,5D-Stacking-Technologien, neuartige ESD-Tests und die Bewertung von ESD-Kontrollprozessen.

Shih-Hung Chen (Masters 2002; PhD 2009) ist seit 2010 in der Device Reliability and Electric Characterization (DRE) Group bei imec tätig, seit 2019 als ESD-Teamleiter und Principal Member of Technical Staff (PMTS). Er ist Autor oder Co-Autor von mehr als 100 Konferenz- und Zeitschriftenpublikationen. Seine aktuellen Forschungsinteressen umfassen ESD-Schutzmaßnahmen in fortgeschrittenen Sub-5nm-Technologieknoten, in 3D/2,5D-IC-Anwendungen und in Design Technology Co-Optimization (DTCO), System Technology Co-Optimization (STCO) mit der Integration von III-V-Verbindungen.

Literatur

[1] ‘Next to FinFET, how will ESD suffer?’, ESD Association, blogpost by imec, July 2021

[2] ‘ESD challenges in 300nm Si substrate of DTCO/STCO scaling options,’ W.-C. Chen et al., IEDM 2023

[3] ‘Upcoming challenges of ESD reliability in DTCO with BS-PDN routing via BPRs’, W.-C. Chen et al., VLSI 2023

[4] ‘How to power chips from the backside: benefits and building blocks of a backside power delivery network,’ imec Reading Room.

[5] ‘Enabling active backside technology for ESD and LU reliability in DTCO/STCO,’ K. Serbulova et al., VLSI 2022

(ID:49935373)

:quality(80)/p7i.vogel.de/wcms/02/46/0246a163cd4f770fc4ec4707eed026a3/0118485226.jpeg)

:quality(80)/p7i.vogel.de/wcms/1d/33/1d33974fef7933ea30c16340eebef3c9/0118272751.jpeg)

:quality(80)/p7i.vogel.de/wcms/de/e9/dee92adb2d0ccca12fc131b4b55a4c51/0118262284.jpeg)

:quality(80)/p7i.vogel.de/wcms/56/3d/563df7482bac59034c2c1ba6949eabeb/0118519606.jpeg)

:quality(80)/p7i.vogel.de/wcms/04/e7/04e7948f02e1d792f245d19fbb6f84be/0118504854.jpeg)

:quality(80)/p7i.vogel.de/wcms/03/c5/03c5925ec95a2630b71e941343a128c5/0118433867.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/76/0d76806079a5a3d36aacdb006a7aba5a/0118407519.jpeg)

:quality(80)/p7i.vogel.de/wcms/7e/bb/7ebbb9e0afa7f66bd9abed55322eb88e/0118350007.jpeg)

:quality(80)/p7i.vogel.de/wcms/0f/89/0f89b224c4b3bb6fda7cbec9c56d9072/0118533982.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/0d/1a0d73826922a88118e8f6e04799665d/0118425986.jpeg)

:quality(80)/p7i.vogel.de/wcms/72/5f/725fbe6121731518e12f6d0b8d7397cd/0118433936.jpeg)

:quality(80)/p7i.vogel.de/wcms/43/a5/43a5630d2a63fbe82f29e17b71d5dcb3/0118499684.jpeg)

:quality(80)/p7i.vogel.de/wcms/74/47/7447ac45f80368ce7f86b76af1c6da99/0118407224.jpeg)

:quality(80)/p7i.vogel.de/wcms/ce/39/ce39569b6845cb072030fdf6505fb7c5/0118404058.jpeg)

:quality(80)/p7i.vogel.de/wcms/c9/22/c9228b8ec955c03dc075e8875f4cabf8/0117754897.jpeg)

:quality(80)/p7i.vogel.de/wcms/07/6f/076f09c7a697f193091a6e6be846aef1/0117862638.jpeg)

:quality(80)/p7i.vogel.de/wcms/30/51/305138abdaeda721646661bf6ac4fdbd/0117756540.jpeg)

:quality(80)/p7i.vogel.de/wcms/3c/b9/3cb980e98baaaadddf69a5dad4ad20a0/0117334644.jpeg)

:quality(80)/p7i.vogel.de/wcms/31/8c/318c8c9e8d61814564d11967ccc14c04/0118494408.jpeg)

:quality(80)/p7i.vogel.de/wcms/eb/6c/eb6c99643aca684c44f5ad0411d71f3f/0118318941.jpeg)

:quality(80)/p7i.vogel.de/wcms/79/4b/794b7d23361d39306753a0abab662274/0117836261.jpeg)

:quality(80)/p7i.vogel.de/wcms/84/64/846421e1abb64717319a401a350ed9ff/0118471925.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/06/b606e1899c3d19b8ac0bf5cdada67cd8/0118340949.jpeg)

:quality(80)/p7i.vogel.de/wcms/42/a0/42a0d035baeb02bf4467dd19ad99f583/0118352721.jpeg)

:quality(80)/p7i.vogel.de/wcms/36/94/36944586a51513ee0dc4cbb1fa410689/0118252602.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/bc/9cbcc8436fa8e226234cebdd1a101d61/0118377191.jpeg)

:quality(80)/p7i.vogel.de/wcms/70/91/7091aed6e9292abc5451815f9499984b/0118509991.jpeg)

:quality(80)/p7i.vogel.de/wcms/08/de/08de3cefb97266232f475bb011d9b0c6/0118162151.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/59/e15978926ae2637c5cc1cb07fc9428a6/0118508628.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/66/c266c5cfbc51fb7d06557ee079d406bf/0116839110.jpeg)

:quality(80)/p7i.vogel.de/wcms/3a/1a/3a1a267224e51b795ccc6b8df959f18e/0115998041.jpeg)

:quality(80)/p7i.vogel.de/wcms/3d/14/3d1447535880e284712d1daba8d7d466/0115848899.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/5e/4d/5e4d1371cff23/logo.jpg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/125700/125709/65.png)

:quality(80)/p7i.vogel.de/wcms/a8/e5/a8e5ef8de6629613d69e830d3a3ef14f/0116895212.jpeg)

:quality(80)/p7i.vogel.de/wcms/41/c6/41c6d0b64ef1586a9998cb806a227619/0116895210.jpeg)

:quality(80)/p7i.vogel.de/wcms/a6/7f/a67f5f73946d101967366f5e52307406/0116895211.jpeg)

:quality(80)/p7i.vogel.de/wcms/74/e9/74e9a11a3a3ecbf50485cd6915713613/0116895209.jpeg)

:quality(80)/p7i.vogel.de/wcms/e3/d8/e3d854dc6e4baa56a4345b4b1f732b8a/0114015210.jpeg)

:quality(80)/p7i.vogel.de/wcms/de/89/de8956f8a3c454ac651a8ffa3303c89f/0117868030.jpeg)