Für eigene Mikrocontroller Renesas hat RISC-V-CPU-Kern mit 32-Bit entwickelt

Anbieter zum Thema

Der japanische Chiphersteller baut bereits Mikrocontroller mit proprietären CPUs (RX-Familie) und mit Prozessorkernen von Arm (RA-Serie). Bald werden Modelle mit selbst entwickelten 32-Bit-RISC-V-Kernen das eigene Embedded-Processing-Portfolio erweitern.

Um die Open-Source-Befehlssatzarchitektur RISC-V (Instruction Set Architecture, ISA) ist es in den letzten Monaten etwas ruhiger geworden – zumindest in der Berichterstattung. Das heißt aber nicht, dass in den Entwicklungslabors der Hersteller nicht eifrig an darauf basierenden Produkten gefeilt wird. Aktuelles Beispiel: Renesas Electronics. Der japanische Mikrocontrollerspezialist und Halbleiterhersteller hat einen RISC-V-Prozessorkern entwickelt, der mit 32 Bit arbeitet und im eigenen Controller-Portfolio zum Einsatz kommen soll.

Nach eigenen Angaben stellt Renesas „mit Vorsprung in der Branche die erste Generation eines eigenen RISC-V-CPU-Kerns mit 32-Bit vor“ und positioniert sich „als Marktführer im aufstrebenden RISC-V-Markt“. Das ist nicht korrekt. Vielmehr reiht sich das Unternehmen ein in die Reihe der Firmen, die unabhängig 32-Bit-RISC-V-Produkte für den kommerziellen Einsatz entwickeln.

Viele Hersteller setzen bereits auf die offene ISA

Zum Beispiel Andes Technology: Die „AndesCore“-CPU-IP des RISC-V-Entwicklers kommt bereits in vielen kommerziellen Produkte zum Einsatz – darunter 32-Bit-ASSP-Bausteine für Sprach- und Motorsteuerung sowie die 64-Bit-General-Purpose-Mikroprozessoren (MPUs) RZ/Five von Renesas.

FPGA-Anbieter Efinix hatte Anfang 2022 bereits die zweite Generation seines RISC-V-Prozessors Sapphire mit fünfstufiger Pipeline veröffentlicht. Die RISC-V-SoCs von Efinix basieren auf dem VexRiscv-Kern. Dieser Kern ist eine 32-Bit-CPU auf Basis von RISCV32I mit Erweiterungen für Integer (I), Multiplikationen und Divisionen (M), Atomic-Befehlen (A), Gleitkommaoperationen (F) und Double-Precision (D). Diese Erweiterungen I, M, A, F, und D werden im RISC-V-Sprachgebrauch auch unter dem Kürzel G zusammengefasst.

Ein weiterer FPGA-Anbieter, der auf RISC-V setzt, ist Microchip: Die PolarFire-SoC-FPGAs des Herstellers haben ein fünfkerniges, Linux-fähiges Prozessor-Subsystem, das auf der RISC-V-Befehlssatzarchitektur basiert, sowie ein großes, flexibles L2-Speicher-Subsystem. Die Bausteine umfassen 25-k- bis 460-k-Logikelemente und sollen bis zu 50 Prozent weniger Strom aufnehmen als vergleichbare FPGAs.

Auch das Fraunhofer IPMS hat einen 32-Bit-RISC-V-Prozessor entwickelt: Der „EMSA5“ ist mit einer fünfstufigen Pipeline ausgestattet und soll sowohl in Embedded-Systemen als auch in Anwendungen funktionaler Sicherheit etwa im Automobilbereich eingesetzt werden. Dafür verfügt der IP-Core bereits über eine ASIL-D-ready-Zertifizierung nach der ISO 26262.

Renesas: Erster MCU-Hersteller mit eigenem RISC-V-Kern

Was Renesas meint: Als erster Mikrocontrollerhersteller hat man unabhängig einen RISC-V-Kern entwickelt, der im eigenen MCU-Portfolio eingesetzt werden soll. „Während viele MCU-Anbieter in letzter Zeit gemeinsame Investitionsallianzen gebildet haben, um die Entwicklung von RISC-V-Produkten zu beschleunigen, hat Renesas bereits einen neuen RISC-V-Kern selbst entwickelt“, verkündet das Unternehmen.

Damit beziehen sich die Japaner offensichtlich auf die Ankündigung von Bosch, Infineon, Nordic Semi, NXP und Qualcomm. Die fünf Branchengrößen wollen ein in Deutschland ansässiges Joint Venture aufbauen, das die Verbreitung des RISC-V-Ökosystems weltweit vorantreiben soll. Im Fokus steht hier zunächst der Automobilmarkt, später sollen die Bereiche Mobilgeräte und IoT hinzukommen.

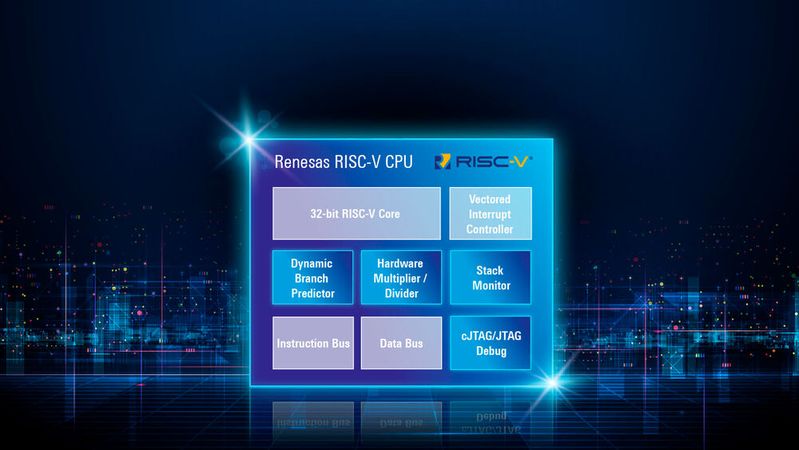

Jetzt also Renesas. Dessen neuer RISC-V-CPU-Kern ergänzt das bestehende IP-Portfolio an 32-Bit-Mikrocontrollern (MCUs), darunter die proprietäre RX-Familie sowie die RA-Familie auf Basis der Arm-Cortex-M-Architektur. Nach eigenen Angaben kann „die vielseitige CPU als Hauptanwendungscontroller, als ergänzender Sekundär-Core in SoCs, On-Chip-Subsystemen oder sogar in Deep Embedded ASSPs eingesetzt werden“.

Die RISC-V-CPU von Renesas erreicht nach eigenen Angaben eine Leistung von 3,27 CoreMark/MHz und „übertrifft damit ähnliche Architekturen auf dem Markt“. Sie enthalte Erweiterungen, „die die Leistung verbessern und gleichzeitig die Codegröße reduzieren“. Renesas sieht seine Neuentwicklung als eine offene und flexible Plattform für IoT, Unterhaltungselektronik, Gesundheitswesen und Industriesysteme.

Ausgewählte Kunden erhalten bereits Bausteinmuster, die auf dem neuen Kern basieren. Die Markteinführung seiner ersten RISC-V-basierten MCU und der dazugehörigen Entwicklungstools ist für das erste Quartal 2024 geplant. Weitere Details will der Hersteller derzeit noch nicht preisgeben.

RISC-V-Chips weltweit milliardenfach im Einsatz

Ohne Frage hat die RISC-V-Technik im Hype Cycle längst die „Aufschrei-Phase“ hinter sich gelassen und sich etabliert. Immer mehr darauf basierende Produkte kommen in den Handel. Laut RISC-V Foundation wurden schon mehr als 10 Milliarden Chips damit produziert. Meistens sind dies jedoch simple 32-Bit-Kerne (RV32) für Embedded-Mikrocontroller, die energieeffizient ausreichend Rechenleistung bereitstellen – etwa Festplatten-Controller. Für Hochleistungschips taugt die ISA bislang nur bedingt.

Besonders beliebt ist RISC-V in China. Hier bietet die ISA den Chipherstellern die Möglichkeit, eigene Prozessoren zu entwickeln, ohne Lizenzgebühren an Chipdesigner Arm zahlen zu müssen. Die IP des Marktführers unterliegt zudem in einigen Fällen US-amerikanischen und britischen Exportbeschränkungen, etwa die besonders rechenstarken Neoverse-V-CPUs. Neoverse V fällt unter das Wassenaar-Abkommen – eine multilaterale Vereinbarung, an der 42 Länder beteiligt sind und die verhindern soll, dass Technologien mit doppeltem Verwendungszweck („dual use“) für militärische Zwecke eingesetzt werden. Arm braucht daher eine Ausfuhrgenehmigung der USA und des Vereinigten Königreichs, um die Technologie zu verkaufen. (me)

:quality(80)/p7i.vogel.de/wcms/d9/63/d96387759311e3826c06d13eb5b47fd7/72601074.jpeg)

Wie funktioniert RISC-V? Grundlagen der offenen Befehlssatzarchitektur

:quality(80)/p7i.vogel.de/wcms/6a/2f/6a2f167401f10f18afdc55b0e90536f9/0109274310.jpeg)

Architektur

10 Techniken für kompakten Code in RISC-V-basierten Anwendungen

:quality(80)/p7i.vogel.de/wcms/b8/86/b8866ca0e23d633df655a4bb5cf912c8/0103259080.jpeg)

Analyse

Darum pusht Intel RISC-V mit einer Milliarde US-Dollar

(ID:49822357)

:quality(80)/p7i.vogel.de/wcms/02/46/0246a163cd4f770fc4ec4707eed026a3/0118485226.jpeg)

:quality(80)/p7i.vogel.de/wcms/1d/33/1d33974fef7933ea30c16340eebef3c9/0118272751.jpeg)

:quality(80)/p7i.vogel.de/wcms/de/e9/dee92adb2d0ccca12fc131b4b55a4c51/0118262284.jpeg)

:quality(80)/p7i.vogel.de/wcms/56/3d/563df7482bac59034c2c1ba6949eabeb/0118519606.jpeg)

:quality(80)/p7i.vogel.de/wcms/04/e7/04e7948f02e1d792f245d19fbb6f84be/0118504854.jpeg)

:quality(80)/p7i.vogel.de/wcms/03/c5/03c5925ec95a2630b71e941343a128c5/0118433867.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/76/0d76806079a5a3d36aacdb006a7aba5a/0118407519.jpeg)

:quality(80)/p7i.vogel.de/wcms/7e/bb/7ebbb9e0afa7f66bd9abed55322eb88e/0118350007.jpeg)

:quality(80)/p7i.vogel.de/wcms/0f/89/0f89b224c4b3bb6fda7cbec9c56d9072/0118533982.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/0d/1a0d73826922a88118e8f6e04799665d/0118425986.jpeg)

:quality(80)/p7i.vogel.de/wcms/72/5f/725fbe6121731518e12f6d0b8d7397cd/0118433936.jpeg)

:quality(80)/p7i.vogel.de/wcms/43/a5/43a5630d2a63fbe82f29e17b71d5dcb3/0118499684.jpeg)

:quality(80)/p7i.vogel.de/wcms/74/47/7447ac45f80368ce7f86b76af1c6da99/0118407224.jpeg)

:quality(80)/p7i.vogel.de/wcms/ce/39/ce39569b6845cb072030fdf6505fb7c5/0118404058.jpeg)

:quality(80)/p7i.vogel.de/wcms/c9/22/c9228b8ec955c03dc075e8875f4cabf8/0117754897.jpeg)

:quality(80)/p7i.vogel.de/wcms/07/6f/076f09c7a697f193091a6e6be846aef1/0117862638.jpeg)

:quality(80)/p7i.vogel.de/wcms/30/51/305138abdaeda721646661bf6ac4fdbd/0117756540.jpeg)

:quality(80)/p7i.vogel.de/wcms/3c/b9/3cb980e98baaaadddf69a5dad4ad20a0/0117334644.jpeg)

:quality(80)/p7i.vogel.de/wcms/31/8c/318c8c9e8d61814564d11967ccc14c04/0118494408.jpeg)

:quality(80)/p7i.vogel.de/wcms/eb/6c/eb6c99643aca684c44f5ad0411d71f3f/0118318941.jpeg)

:quality(80)/p7i.vogel.de/wcms/79/4b/794b7d23361d39306753a0abab662274/0117836261.jpeg)

:quality(80)/p7i.vogel.de/wcms/84/64/846421e1abb64717319a401a350ed9ff/0118471925.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/06/b606e1899c3d19b8ac0bf5cdada67cd8/0118340949.jpeg)

:quality(80)/p7i.vogel.de/wcms/42/a0/42a0d035baeb02bf4467dd19ad99f583/0118352721.jpeg)

:quality(80)/p7i.vogel.de/wcms/36/94/36944586a51513ee0dc4cbb1fa410689/0118252602.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/bc/9cbcc8436fa8e226234cebdd1a101d61/0118377191.jpeg)

:quality(80)/p7i.vogel.de/wcms/70/91/7091aed6e9292abc5451815f9499984b/0118509991.jpeg)

:quality(80)/p7i.vogel.de/wcms/08/de/08de3cefb97266232f475bb011d9b0c6/0118162151.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/59/e15978926ae2637c5cc1cb07fc9428a6/0118508628.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/66/c266c5cfbc51fb7d06557ee079d406bf/0116839110.jpeg)

:quality(80)/p7i.vogel.de/wcms/3a/1a/3a1a267224e51b795ccc6b8df959f18e/0115998041.jpeg)

:quality(80)/p7i.vogel.de/wcms/3d/14/3d1447535880e284712d1daba8d7d466/0115848899.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/5e/e8/5ee8685f55961/duagon-logo-without-r.png)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/119600/119672/65.png)

:fill(fff,0)/p7i.vogel.de/companies/62/5e/625ea073a6efe/eepd-just-embedded-4zu1.jpeg)

:quality(80)/p7i.vogel.de/wcms/f5/f6/f5f6299c928b67cc34a7c24219a70fab/0115011871.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/89/c7895eac53b0d3fe3da56866b1f21578/0113132105.jpeg)