CMOS-Prozesstechnik 1 nm im Blick: Hochtechnologie für tiefe Kontakte auf Nano-Chipstrukturen

Anbieter zum Thema

Auf dem Weg zum 1-nm-Technologieknoten stoßen bislang bewährte Verfahrensschritte in der Halbleiterfertigung an ihre Grenzen. Zum Beispiel die Kupfer-Dual-Damascene-Integration zum Kontaktieren der aktiven Schichten eines Chips. Das Imec hat einen potenziellen Nachfolger für die Metallisierung auf Basis von Ruthenium entwickelt.

Vielschichtig: Bei der Prozesstechnik haben im Wortsinn winzige Optimierungen oft enorme Auswirkungen auf die Leistungsfähigkeit des Gesamtkonstrukts, sprich: der integrierten Schaltung. Sie sind zudem die Voraussetzung für die Evolution der Prozesstechnik hin zu Technologieknoten von 1 nm – und darüber hinaus. Seit mehr als 20 Jahren ist die Kupfer-Dual-Damascene-Integration (siehe Kasten unten) in der Chipfertigung das Arbeitspferd für den Aufbau zuverlässiger elektrischer Verbindungen bei der Hochintegration auf CMOS-Substraten.

Wenn jedoch die Skalierung der Strukturen voranschreitet und die Metallabstände kleiner als 20 nm werden, stößt das Verfahren mehr und mehr an technologische Grenzen: Der unerwünschte, also parasitäre Kapazitätsanteil im Back-End-of-Line (BEOL, siehe Anmerkung unten) steigt unweigerlich auf Werte, die die elektrischen Signale erheblich beeinflussen. Das Widerstandskapazitätsprodukt (RC) begrenzt die mögliche Schaltfrequenzen und führt zu Signalverzögerungen. Wissenschaftler suchen daher bereits seit einigen Jahren nach alternativen Integrationsschemata und Metallen, die bei sehr engen Metallabständen bessere Performance-Werte aufweisen.

Praktikable Alternative für das Arbeitspferd der Chipfertigung

Vor etwa fünf Jahren schlug das Imec-Forschungs- und Innovationsinstitut Semi-Damascene als praktikable Alternative zu Cu-Dual-Damascene zunächst für die Integration der kritischsten lokalen (Mx) Verbindungsschichten der 1-nm-Technologieknoten (und darüber hinaus) vor. Neuste Ergebnisse haben Gayle Murdoch, leitende technische Mitarbeiterin am Imec, und Zsolt Tokei, Imec Fellow und Program Director Nano-Interconnects, auf dem 2022 IEEE VLSI Symposium on Technology and Circuits (VLSI 2022) Ende Juni präsentiert.

Ziel der vorgestellten Technologie ist es, den Anstieg des Widerstands-Kapazitäts-Faktors (RC) zukünftiger Verbindungen durch direkte Metallstrukturierung einzudämmen. Die Demonstration des Imec hat nach Angaben des Instituts erstmals experimentell gezeigt, dass die semi-damaszenische Verarbeitung von Ruthenium (Ru) mit einem hohen Seiten- beziehungsweise Aspektverhältnis von AR=6 zu einer Reduzierung des Widerstands um etwa 40 % gegenüber AR=3 führt – ohne dass dabei mehr Fläche benötigt wird. Zusätzliche Simulationen bestätigen laut Tokei die Vorteile auf Schaltungsebene in Kombination mit Luftspalten als Dielektrikum.

Eine ergänzende experimentelle Studie zeige außerdem, dass die Zuverlässigkeit von Semi-Damascene mit Airgaps im Vergleich zu Dual-Damascene mit Low-k-Dielektrika vergleichbar ist. Hinzu kommt laut Tokei, dass der Semi-Damascene-Flow mit Luftspalt zuverlässig ist und eine Lebensdauer der Schaltung von mehr als 10 Jahren ermöglicht.

Einführung der Semi-Damascene-Integration in die Back-End-of-Line-Roadmap

Im Gegensatz zum Dual-Damascene-Verfahren beruht die Semi-Damascene-Integration auf der direkten Strukturierung des Verbindungsmetalls zur Herstellung der Leitungen (sogenannte subtraktive Metallisierung). Es ist kein chemisch-mechanisches Polieren (CMP) des Metalls zur Vervollständigung des Prozessablaufs erforderlich. Die Durchkontaktierungen, die die nachfolgenden Verbindungsschichten miteinander verbinden, werden nach dem Prinzip des Single-Damascene-Verfahrens strukturiert, dann mit Metall gefüllt und überfüllt – das heißt, dass die Metallabscheidung fortgesetzt wird, bis eine Metallschicht über dem Dielektrikum entsteht.

Diese Metallschicht wird dann maskiert und geätzt, um die zweite Verbindungsschicht zu bilden. Nach der Metallstrukturierung können die Lücken zwischen den Leitungen mit einem Dielektrikum aufgefüllt oder zur Bildung von (partiellen) Luftspalten in den lokalen Schichten verwendet werden. Wie beim herkömmlichen Dual-Damascene-Ansatz werden bei einem Semi-Damascene-Flow zwei Schichten (Via und Top-Metall) in einem Durchgang gebildet. Dies macht die Semi-Damascene im Vergleich zur Dual-Damascene effektiv kostengünstiger.

Vorteile einer Semi-Damascene-Integrationsfolge

Semi-Damascene verspricht mehrere Vorteile gegenüber Cu-Dual-Damascene bei engen Metallabständen. Zsolt Tokei erklärt: „Erstens ermöglicht es höhere Leitungsquerschnitte bei gleichzeitiger Kontrolle der Kapazität, was insgesamt einen RC-Vorteil verspricht. Zweitens führt das Fehlen eines Metall-CMP-Schrittes zu einem vereinfachten und kostengünstigeren Integrationsschema. Schließlich erfordert die Semi-Damascene-Integration ein barrierefreies, strukturierbares Metall wie Wolfram (W), Molybdän (Mo) oder Ruthenium (Ru).

Durch die Verwendung von Metallen, die im Gegensatz zu Cu keine Metallbarriere benötigen, kann der wertvolle leitende Bereich vollständig durch das Verbindungsmetall selbst genutzt werden. Dies gewährleistet einen wettbewerbsfähigen Durchgangswiderstand bei skalierten Abmessungen. Neben den Vorteilen gibt es natürlich zahlreiche Herausforderungen zu bewältigen, bevor sich ein solches System in der Industrie durchsetzen kann. Ein Schritt in diese Richtung ist die tatsächliche Demonstration eines Zwei-Metall-Schemas. Während die Vorteile bisher nur durch Simulation und Modellierung aufgezeigt wurden, hat Imec zum ersten Mal einen experimentellen Nachweis mit einem Zwei-Metall-Level-Halb-Damascene-Modul erbracht.

Vollständig selbstausrichtende Durchkontaktierung – ein kritischer Baustein

Bei Metallabständen von nur 20 nm ist die kontrollierte Landung der Vias (Durchkontaktierungen) auf den schmalen Leitungen der Schlüssel zum erfolgreichen Einsatz des Semi-Damascene-Integrationsmoduls. Wenn das Via und die Leitungen (sowohl am oberen als auch am unteren Ende des Vias) nicht richtig ausgerichtet sind, besteht die Gefahr von Leckagen zwischen dem Via und einer benachbarten Leitung. Diese Leckagepfade sind das Ergebnis eines zu großen Überlagerungsfehlers, der durch die konventionelle Strukturierung der kleinen Via-Löcher verursacht wird.

Gayle Murdoch, leitende technische Mitarbeiterin bei Imec: „Einen Weg zu finden, um funktionale, vollständig selbst ausgerichtete Durchkontaktierungen herzustellen, war ein heiliger Gral des Semi-Damascene-Prozesses. Wir haben diesen Meilenstein durch intensive Zusammenarbeit zwischen den Integrations-, Lithographie-, Ätz- und Reinigungsgruppen am Imec erreicht. Mit unserem vollständig selbstausgerichteten Integrationsschema konnten wir Überlagerungsfehler von bis zu 5 nm kompensieren – ein wichtiger Erfolg.“

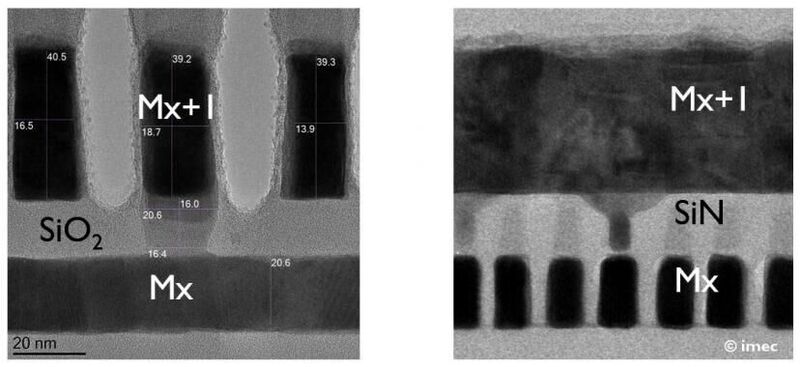

Die untere Selbstausrichtung wurde durch die selektive Entfernung von Siliziumnitrid nach dem Füllen der Lücken sichergestellt, so dass sich das Via an den Grenzen der unteren Metalllinie bilden konnte. Die Selbstausrichtung zur oberen Metallschicht (Ru) wurde durch den Ru-Überätzungsschritt erreicht, der nach dem Via-Overfill und der Ru-Strukturierung erfolgte.

Geringer Widerstand und Zuverlässigkeit bei 18 nm Pitch

Die Anwendung des subtraktiven Ätzens von Ru mit vollständig selbstausgerichteten Durchkontaktierungen führte zu einem funktionsfähigen Bauteil mit zwei Metallebenen und einem Metallabstand von nur 18 nm. Die EUV-Lithografie (Extrem Ultraviolett) in Kombination mit der selbstausrichtenden Doppelstrukturierung (SADP) wurde für die Strukturierung der 9 nm breiten unteren lokalen Ru-Verbindungslinie (Mx) verwendet, während die EUV-Lithografie mit Einzelbelichtung für den Druck der oberen Schicht (Mx+1) und des Durchgangs verwendet wurde. Das obere Metall wurde mit Luftspalten kombiniert, um der Kapazitätserhöhung entgegenzuwirken.

Beim Vergleich des Leitungswiderstands mit der leitenden Fläche von Ru und Cu zeigt sich, dass Ru bei den Zielmetallabständen deutlich besser abschneidet als Cu. Die Selbstausrichtung der Vias konnten die Forscher sowohl morphologisch als auch elektrisch bestätigen. Der Via-Widerstand liegt zwischen 40 und 60 Ω für 26-18nm Metallabstand, die Durchbruchfeldstärke vom Via zur Leitungsschicht bei > 9 MV/cm.

„Semi-Damascene ist eine würdige Alternative zu Dual-Damascene“

Zsolt Tokei freut sich: „Wir haben hervorragende Werte für alle wichtigen technischen Parameter, einschließlich Durchgangs- und Leitungswiderstand und Zuverlässigkeit, nachgewiesen.“ Dies zeige, dass Semi-Damascene eine würdige Alternative zu Dual-Damascene für die Integration der ersten drei lokalen Verbindungsebenen bei einem 1-nm-Technologieknoten sei – und darüber hinaus. „Unser Zwei-Metall-Level-Bauelement mit vollständig selbstausrichtendem Via hat sich als ein wichtiger Baustein erwiesen.“

Weitere Verbesserungen seien möglich, indem das Seitenverhältnis der Leitungen erhöht wird (was den Widerstand reduziert), während die Luftspalte beibehalten werden (was die Kapazität unter Kontrolle hält). Gleichzeitig hat Imec konkrete Ideen für die Implementierung von Middle-of-Line- (MOL) und BEOL-Technologie-Boostern unter Verwendung der Semi-Damascene-Technologie, die eine weitere Flächenreduzierung auf Standardzellenebene ermöglichen soll.

Was ist Damascene-Integration?

„Damascening“ oder deutsch „Damaszenierung“ bezeichnet ursprünglich eine antike Verzierungstechnik: Bei dieser auch Tauschierung genannten Technik wird metallisches Material in Vertiefungen eingebracht, die zuvor in das zu verzierende Objekt eingearbeitet wurden – beispielsweise einen Dolch.

In der CMOS-Prozesstechnik gibt es bei der Herstellung von integrierten Schaltkreisen (Mikrochips) vergleichbare Verfahrensschritte, weshalb man den Namen auch dafür verwendet: Hier werden Löcher oder Bahnen in zuvor aufgebrachte Isolationsschichten geätzt, die dann mit einem leitfähigen Material gefüllt werden. So entsteht eine vertikale Durchkontaktierung (auch Via genannt) zu darunterliegenden Schichten, etwa Leiterbahnen oder Transistoren. Angesichts der winzigen Dimensionen von wenigen Nanometern haben die Eigenschaften der eingesetzten Materialien massiven Einfluss auf die Leistungsfähigkeit der gesamten Schaltung.

Das heute meistverwendete Dual-Damascene-Verfahren ist eine Weiterentwicklung des einfachen Damascene-Prozesses, bei dem meist Kupfer (Cu) für die Metallisierungsebene zum Einsatz kommt. Der Zusatz Dual rührt daher, dass durch eine Folge mehrerer Verfahrensschritte Leiterbahnen und Vias quasi in einem Zug realisiert werden.

Durch das verwendete Material, die Höhe und Breite der Vias sowie deren Abstand zueinander lassen sich die elektrischen Eigenschaften dieser essenziellen Building Blocks von integrierten Schaltungen gezielt beeinflussen. Durch die zunehmende Miniaturisierung steigt der Einfluss parasitärer Effekte – etwa von Kapazitäten – und wird zunehmend zum Problem.

Anmerkung

1. BEOL steht für „back end of line“ und bezeichnet den letzten Abschnitt in der Halbleiterfertigung, also die obersten Schichten ab der Abscheidung der metallischen Zwischenschichten bis zur Fertigstellung.

2. FEOL steht für „Front End of Line“ und bezeichnet den ersten Abschnitt in der Halbleiterfertigung, in dem die Bauelemente im Substrat dotiert und strukturiert werden, bevor die metallischen Verbindungsschichten aufgebracht werden.

:quality(80)/images.vogel.de/vogelonline/bdb/1499200/1499202/original.jpg)

Neuartige Interconnects: SuperVias revolutionieren Chipdesign

:quality(80)/images.vogel.de/vogelonline/bdb/1844300/1844386/original.jpg)

Logikintegration jenseits von 2 Nanometer

„CMOS-Skalierung ist noch lange nicht am Ende“

:quality(80)/p7i.vogel.de/wcms/ff/bc/ffbc4db7e0401b8eaf494bc4401b668d/99657019.jpeg)

Roadmap der Logiktechnologie, Teil 1

CMOS: Auf dem Weg zum 1-nm-Prozessknoten

(ID:48462397)

:quality(80)/p7i.vogel.de/wcms/02/46/0246a163cd4f770fc4ec4707eed026a3/0118485226.jpeg)

:quality(80)/p7i.vogel.de/wcms/1d/33/1d33974fef7933ea30c16340eebef3c9/0118272751.jpeg)

:quality(80)/p7i.vogel.de/wcms/de/e9/dee92adb2d0ccca12fc131b4b55a4c51/0118262284.jpeg)

:quality(80)/p7i.vogel.de/wcms/56/3d/563df7482bac59034c2c1ba6949eabeb/0118519606.jpeg)

:quality(80)/p7i.vogel.de/wcms/04/e7/04e7948f02e1d792f245d19fbb6f84be/0118504854.jpeg)

:quality(80)/p7i.vogel.de/wcms/03/c5/03c5925ec95a2630b71e941343a128c5/0118433867.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/76/0d76806079a5a3d36aacdb006a7aba5a/0118407519.jpeg)

:quality(80)/p7i.vogel.de/wcms/7e/bb/7ebbb9e0afa7f66bd9abed55322eb88e/0118350007.jpeg)

:quality(80)/p7i.vogel.de/wcms/0f/89/0f89b224c4b3bb6fda7cbec9c56d9072/0118533982.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/0d/1a0d73826922a88118e8f6e04799665d/0118425986.jpeg)

:quality(80)/p7i.vogel.de/wcms/72/5f/725fbe6121731518e12f6d0b8d7397cd/0118433936.jpeg)

:quality(80)/p7i.vogel.de/wcms/43/a5/43a5630d2a63fbe82f29e17b71d5dcb3/0118499684.jpeg)

:quality(80)/p7i.vogel.de/wcms/74/47/7447ac45f80368ce7f86b76af1c6da99/0118407224.jpeg)

:quality(80)/p7i.vogel.de/wcms/ce/39/ce39569b6845cb072030fdf6505fb7c5/0118404058.jpeg)

:quality(80)/p7i.vogel.de/wcms/c9/22/c9228b8ec955c03dc075e8875f4cabf8/0117754897.jpeg)

:quality(80)/p7i.vogel.de/wcms/07/6f/076f09c7a697f193091a6e6be846aef1/0117862638.jpeg)

:quality(80)/p7i.vogel.de/wcms/30/51/305138abdaeda721646661bf6ac4fdbd/0117756540.jpeg)

:quality(80)/p7i.vogel.de/wcms/3c/b9/3cb980e98baaaadddf69a5dad4ad20a0/0117334644.jpeg)

:quality(80)/p7i.vogel.de/wcms/31/8c/318c8c9e8d61814564d11967ccc14c04/0118494408.jpeg)

:quality(80)/p7i.vogel.de/wcms/eb/6c/eb6c99643aca684c44f5ad0411d71f3f/0118318941.jpeg)

:quality(80)/p7i.vogel.de/wcms/79/4b/794b7d23361d39306753a0abab662274/0117836261.jpeg)

:quality(80)/p7i.vogel.de/wcms/84/64/846421e1abb64717319a401a350ed9ff/0118471925.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/06/b606e1899c3d19b8ac0bf5cdada67cd8/0118340949.jpeg)

:quality(80)/p7i.vogel.de/wcms/42/a0/42a0d035baeb02bf4467dd19ad99f583/0118352721.jpeg)

:quality(80)/p7i.vogel.de/wcms/36/94/36944586a51513ee0dc4cbb1fa410689/0118252602.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/bc/9cbcc8436fa8e226234cebdd1a101d61/0118377191.jpeg)

:quality(80)/p7i.vogel.de/wcms/70/91/7091aed6e9292abc5451815f9499984b/0118509991.jpeg)

:quality(80)/p7i.vogel.de/wcms/08/de/08de3cefb97266232f475bb011d9b0c6/0118162151.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/59/e15978926ae2637c5cc1cb07fc9428a6/0118508628.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/66/c266c5cfbc51fb7d06557ee079d406bf/0116839110.jpeg)

:quality(80)/p7i.vogel.de/wcms/3a/1a/3a1a267224e51b795ccc6b8df959f18e/0115998041.jpeg)

:quality(80)/p7i.vogel.de/wcms/3d/14/3d1447535880e284712d1daba8d7d466/0115848899.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/76800/76895/65.jpg)

:fill(fff,0)/p7i.vogel.de/companies/64/21/64219ce08bf52/logo.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/62/6f/626f9753a3e5a/a-category-images-970x300-logo.jpeg)

:quality(80)/p7i.vogel.de/wcms/59/c8/59c8426a687b84200ef245489e2b6102/0105713009.jpeg)

:quality(80)/p7i.vogel.de/wcms/80/bb/80bb7928ffe6a9b2064256077ee02206/0105713019.jpeg)

:quality(80)/p7i.vogel.de/wcms/fa/67/fa67a4102ac0d65c7dc850ba6299057b/0105713017.jpeg)

:quality(80)/p7i.vogel.de/wcms/d7/75/d7758b284da6a20ee0e9d64f0bbc8897/0105713018.jpeg)

:quality(80)/p7i.vogel.de/wcms/e3/d8/e3d854dc6e4baa56a4345b4b1f732b8a/0114015210.jpeg)

:quality(80)/p7i.vogel.de/wcms/34/2b/342bc2bd91fcd639a4f1b3775c3e69e2/0115996348.jpeg)