Si-spin- und supraleitungsbasierte Quantentechnologien Industrielle Skalierung: Qubits aus der Chip-Fab

Anbieter zum Thema

Kryo-CMOS-Elektronik an der Schnittstelle zu supraleitenden Qubits und ein Chip-Fab-kompatibler Prozess, der auf die wesentlichen Elemente der Hochskalierung von Si-Spin-Qubits abzielt: Es gibt bedeutende Fortschritte bei der Entwicklung von Quantencomputern.

Silizium-Spin-Qubit- und supraleitende Qubit-Plattformen – beides sind geeignete Kandidaten zum Skalieren der Quantentechnologie. Die Kompatibilität mit industriellen Produktionstechniken und das Entwickeln von Steuerungs- und Ausleseelektronik für die steigende Anzahl von Qubits sind zentrale Herausforderungen, wenn es darum geht, Forschungsanstrengungen von der Labor- zur Fabrikumgebung voranzutreiben. Imec hat nun Fortschritte für beide Plattformen vermeldet: Hier Kryo-Elektronik für die Verbindung mit supraleitenden Qubits, dort eine 300-mm-CMOS-Plattform, die auf die Hochskalierung von Schlüsselkomponenten für Si-Spin-Qubits abzielt.

Langfristig soll das Quantencomputing Millionen von rauschfreien Qubits nutzen können, um bestimmte Probleme zu lösen, die mit klassischen Computern nur schwer zu bewältigen sind. Zu den Anwendungsbereichen, die von dieser Technologie profitieren könnten, gehören die Materialsynthese, die pharmazeutische Entwicklung von Medikamenten und die Cybersicherheit, um nur einige zu nennen.

Verschiedene Quantencomputerplattformen mit unterschiedlichen Arten von Qubits werden derzeit untersucht. Weltweit werden Anstrengungen unternommen, um die Anzahl der Qubits von einigen Hundert auf Millionen von Qubits zu erhöhen. Jede Plattform ist unterschiedlich ausgereift und hat ihre eigenen Anforderungen an die Skalierung. Zu den gemeinsamen Herausforderungen gehören eine gut kontrollierte Qubit-Integration in großformatigen Wafer-Anlagen und die Notwendigkeit einer Elektronik, die mit der wachsenden Anzahl von Qubits kommuniziert.

Supraleitende Quantenschaltungen: Schon über 100 Qubits gekoppelt

Supraleitende Quantenschaltungen haben sich als die wohl am weitesten entwickelte Plattform erwiesen. Die Energiezustände supraleitender Qubits sind relativ leicht zu kontrollieren. Forscher konnten bereits mehr als hundert Qubits miteinander koppeln. Dies ermöglicht ein immer höheres Maß an Verschränkung – eine der Säulen des Quantencomputers. Außerdem wurden supraleitende Qubits mit langen Kohärenzzeiten (bis zu mehreren 100 µs) und ausreichend hohen Gattertreuewerten – zwei wichtige Maßstäbe für die Quanteninformatik – in Laborumgebungen weltweit demonstriert.

Im Jahr 2022 haben die Forscher am Imec einen bedeutenden Meilenstein auf dem Weg zur Realisierung eines 300-mm-CMOS-Prozesses für die Herstellung hochwertiger supraleitender Qubits erreicht. Der Nachweis, dass die Herstellung hochleistungsfähiger Qubits mit industriellen Prozessen kompatibel ist, beseitigt die erste grundlegende Hürde für ein Upscaling, d.h. eine verbesserte Variabilität und Ausbeute. Es bleibt die Notwendigkeit, skalierbare Messsysteme zu entwickeln, die mit der wachsenden Zahl rauschempfindlicher supraleitender Qubits zusammenarbeiten.

Langfristig wird viel von Silizium-Spin-basierten Qubits erwartet. Diese Si-Spin-Qubits sind schwerer zu kontrollieren als supraleitende Qubits, aber sie sind deutlich kleiner (Nanometer statt Millimeter). Das ist bei der Skalierung von großem Vorteil. Außerdem ist die Technologie in hohem Maße mit CMOS-Fertigungstechnologien kompatibel und bietet Gleichmäßigkeit im Wafer-Maßstab mit hochentwickelten Back-End-of-Line-(BEOL-)Verbindungen der Si-Quantenpunktstrukturen. Das BEOL bezeichnet die auf das Wafer-Substrat im Laufe des Fertigungsprozesses aufgebrachten Verbindungsschichten. Allerdings weisen Si-basierte Quantenpunktstrukturen, die mit industriellen Fertigungstechniken hergestellt werden, in der Regel ein höheres Ladungsrauschen auf. Ihre geringe physikalische Größe macht auch die Verbindung von Qubit zu Qubit und von Qubit zu klassischer Steuerungslogik schwieriger.

Ein Kryo-CMOS-Multiplexer für das Auslesen und die Steuerung supraleitender Qubits

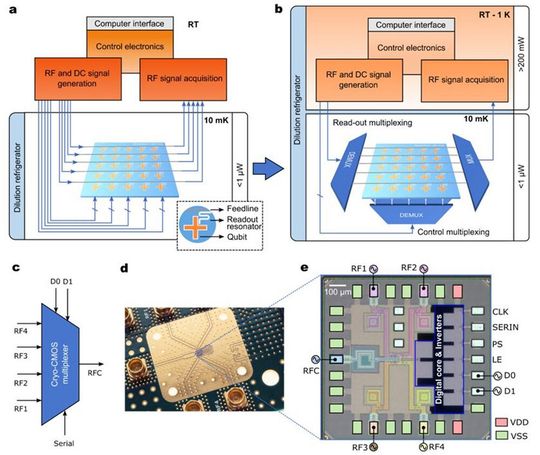

Die erforderliche Zunahme an Qubits erfordert flexible und skalierbare Lösungen, um die Qubits steuern und aussagekräftige Daten auslesen zu können. In den frühen Quantenprozessoren von heute werden externe elektronische Schaltungen mit mindestens einer Steuerleitung pro Qubit verwendet. Diese führt von der Raumtemperaturstufe zur niedrigsten Temperaturstufe des sogenannten „Verdünnungskühlers“ (dilution refrigerator), der die Qubits enthält.

Die Basistemperatur liegt bei supraleitenden Quantencomputersystemen bei nur zehn MilliKelvin (mK). Ein solcher Ansatz kann für bis zu wenigen tausend Qubits verwendet werden. Er ist daher nicht geeignet für große Quantencomputer, die dynamische Schaltkreisoperationen wie die Quantenfehlerkorrektur erfordern. Die Steuer- und Ausleseleitungen tragen nicht nur zu einem massiven E/A-Engpass auf der Ebene der Dilutions-Kältemaschine bei, jeder Draht bringt auch Wärme in das kryogene System ein, so dass das Budget für ihre Kühlung nicht mehr ausreicht.

CMOS-basierte Kryo-Elektronik

Eine attraktive Lösung ist die Verwendung von CMOS-basierter Kryo-Elektronik, die HF-(De-)Multiplexing-Elemente enthält, die bei der Basistemperatur der Verdünnungskühler arbeiten. Eine solche Lösung entschärft den E/A-Engpass, da die Anzahl der Drähte, die von Raum- auf mK-Temperaturen übergehen, erheblich reduziert werden kann. Zum Auslesen würden die Multiplexer es beispielsweise erlauben, dass mehrere Signale von einer Gruppe von Quantengeräten auf eine gemeinsame, auf Basistemperatur liegende Ausgangsleitung der Verdünnungskühler geschaltet werden, bevor sie den Kühlbereich verlassen.

Dieser Ansatz wurde bereits für Si-Spin-Qubit-Quantensysteme demonstriert. Bisher wurde die Kryogenik-Elektronik jedoch noch nicht mit supraleitenden Qubits verbunden, da diese eine wesentlich geringere Toleranz gegenüber hochfrequentem elektromagnetischem Rauschen aufweisen. Ob in Form von Abwärme oder elektromagnetischer Strahlung, Rauschen kann die fragilen Quantenüberlagerungen leicht stören und zu Fehlern führen. Deshalb sollte die Leistungsaufnahme der Multiplexer-Schaltkreise sehr gering sein und deutlich unter dem Kühlungsbudget der Verdünnungskühler liegen. Darüber hinaus müssen die Multiplexer eine gute HF-Leistung aufweisen, z. B. im Hinblick auf Breitbandbetrieb und Schalten im Nanosekundenbereich.

Erfolgreiche Verbindung von supraleitenden Qubits und Kryo-CMOS-Multiplexer

Imec demonstrierte erstmals einen Kryo-CMOS-Multiplexer mit äußerst niedrigem Leistungsbedarf, der bei einer rekordverdächtig niedrigen Temperatur von 10 mK arbeiten kann. Rauschen und Verlustleistung des Mulitplexers sind ausreichend gering. Er wurde erfolgreich mit hochkohärenten supraleitenden Qubits verbunden, um eine Qubit-Kontrolle mit einer Gattertreue von über 99,9% für ein einzelnes Qubit durchzuführen. Diese Zahl quantifiziert den Unterschied zwischen einem idealen Gatter und einem physikalischen Gatter in der Quantenhardware. Sie liegt über dem Schwellenwert für den Start von Experimenten wie der Quantenfehlerkorrektur – eine Voraussetzung für das Realisieren praktischer Quantencomputer, die fehlertolerante Ergebnisse liefern können. Die Ergebnisse wurden in Nature Electronics [1] veröffentlicht.

Imec hat den Multiplexer-Chip kundenspezifisch entwickelt und in einer gewerblichen Foundry unter Verwendung einer 28-nm-Bulk-CMOS-Fertigungstechnologie hergestellt. Die extrem geringe statische Leistungsaufnahme von 0,6 µW (bei einer Bias-Spannung (Vdd) von 0,7 V) wurde durch die weitestgehende Eliminierung oder Modifizierung der leistungshungrigsten Teile einer herkömmlichen Multiplexer-Schaltung erreicht.

:quality(80)/p7i.vogel.de/wcms/0a/5b/0a5bf64da854b87c0d0f47c6b84da8a2/0105773842.jpeg)

Quantencomputer

Interview: Meilenstein bei Quanten-Fehlerkorrektur erreicht

Gleichzeitige Kontrolle mehrerer Qubits innerhalb einer Pulssequenz

Die einfachste Art, den Multiplexer zu betreiben, ist der statische Betriebsmodus, der für die Charakterisierung einzelner Qubits sehr nützlich ist. Operationen mit mehr als einem Qubit – wie die Quantenfehlerkorrektur oder die Kontrolle von Qubits in großem Maßstab – erfordern jedoch einen anderen Ansatz, der die gleichzeitige Kontrolle mehrerer Qubits innerhalb einer Pulssequenz ermöglicht.

Die Imec-Forscher haben eine Lösung entwickelt, bei der die Steuersignale im Zeitmultiplexverfahren verarbeitet werden. Dies könnte eine interessante Grundlage für den Aufbau zukünftiger, groß angelegter Systemarchitekturen für Quantencomputer sein. Vorläufige Experimente zeigen, dass der Multiplexer schnelle dynamische Schaltvorgänge im Nanosekundenbereich durchführen kann und somit in der Lage ist, aktives Zeitmultiplexing zu betreiben, während das Übersprechen der Signale ausreichend unterdrückt wird. Derzeit arbeitet das Team an der Implementierung eines Zwei-Qubit-Gatters, das auf dem Konzept des Zeitmultiplexens basiert.

Ziel der hier beschriebenen Experimente ist das Reduzieren des Verdrahtungsaufwands. Sie können damit einen wichtigen Beitrag zur Entwicklung großer Quantencomputer leisten. Aber sie bringen auch Innovationen auf dem Gebiet der Messtechnik hervor. Bei den Experimenten wurde die ultraniedrige Rauschleistung des Multiplexing-Schaltkreises bei mK-Temperatur zum ersten Mal mit den supraleitenden Qubits von Imec charakterisiert. Mit anderen Worten: Das supraleitende Qubit kann als hochempfindlicher Rauschsensor eingesetzt werden, der die Leistung von Elektronik messen kann, die bei ultratiefen Temperaturen und in bisher unerforschten Rauschbereichen arbeitet.

Für 300-mm-CMOS-Plattform: Modularer Integrationsansatz für Si-Spin-Qubits

Si-Spin-Qubits werden durch Halbleiter-Quantenpunktstrukturen definiert, die einen einzelnen Spin eines Elektrons oder Lochs einfangen. Für eine optimale Spin-Qubit-Kontrolle muss die Qubit-Umgebung ein geringes Ladungsrauschen aufweisen. Die Gate-Elektroden müssen gut definiert sein und kleine Abstände aufweisen, um eine elektrische Abstimmbarkeit zu gewährleisten. Darüber hinaus muss die Spin-Kontrollstruktur für eine schnelle Ansteuerung mit geringer Dephasierung optimiert sein.

High-Fidelity-Si-Spin-Qubits wurden wiederholt in Laborumgebungen mit wenigen Qubits demonstriert. Techniken zur Verarbeitung der Qubit-Nanostrukturen wie das Ablösen von Metall werden sorgfältig ausgewählt, um ein geringes Rauschen in der Qubit-Umgebung zu erreichen. Diese gut kontrollierten Herstellungstechniken haben jedoch einen schwerwiegenden Nachteil: Sie erschweren eine Skalierung auf eine größere Anzahl von Qubits, da sie nicht die erforderliche Homogenität im großen Maßstab erreichen – der eigentliche Grund, warum diese Methoden vor Jahrzehnten in der Halbleiterindustrie allgemein aufgegeben wurden.

:quality(80)/p7i.vogel.de/wcms/4c/73/4c735f4a008030da0bafd34d7abc9120/0104376060.jpeg)

Photonischer Quantencomputerchip „Made in Germany“

Projekt PhoQuant: Quanten-Rechenpower bei Raumtemperatur

Verfahren aus der Chipherstellung auch für Qubit-Hardware nutzbar

Industrielle Fertigungstechniken wie das subtraktive Ätzen und die lithografische Strukturierung können dagegen eine Homogenität im Wafer-Maßstab bieten und ebnen so den Weg für das Hochskalieren der Technologie. Es wurde jedoch beobachtet, dass sie die Qubit-Umgebung mitunter beeinträchtigen. Darüber hinaus sind Qubit-Komponenten, wie die eng beieinander liegenden Gate-Elektroden und die Spin-Kontrollstrukturen, auch keine normalen Transistorstrukturen und weichen daher von den typischen Transistor-Roadmaps ab, was eine (kostspielige) Neuentwicklung erfordert.

Zudem hängt die Qubit-Leistung weitgehend von all diesen Strukturen und von umfassenden Optimierungen des gesamten Gate-Stacks, des Metallelektroden-Designs und der Spin-Kontrollmodule ab, die für die Qubit-Leistung notwendig sind. Dennoch sollte die Gesamtstruktur des Bauelements mit den Herstellungsmethoden kompatibel sein, die für fortschrittliche, skalierte Transistoren in kommerziellen Foundries verwendet werden, um die Chance auf ein Upscaling zu wahren.

Fertigungsparadoxon bei Qubits

Am Imec gehen die Forscher dieses Paradox durch eine sorgfältige Optimierung und Entwicklung des Fab-Qubits in einem modularen Ansatz an: verschiedene Qubit-Elemente werden separat behandelt und als Teil eines „State-of-the-art“-300-mm-Integrationsflusses optimiert, um die Vorwärtskompatibilität mit den Skalierungsanforderungen zu gewährleisten und gleichzeitig den Bedarf an spezieller, nicht standardisierter Bauteiloptimierung zu erfüllen, wie es die anspruchsvolle Quantenumgebung erfordert.

Die vorläufigen Ergebnisse der optimierten Strukturen sind vielversprechend und zeigen, dass die 300-mm-Fab-Integration eine überzeugende Materialplattform für hochwertige Si-basierte Spin-Qubits und Upscaling-Studien ist. Die Entwicklungen profitieren von der unübertroffenen Homogenität der CMOS-Fertigungstechniken [2]. (me)

:quality(80)/p7i.vogel.de/wcms/c3/46/c346a009d8e2cf99408954492b046558/0112553950.jpeg)

Von Europa in die Welt

Modernste Chipfertigung: Imec und ASML bauen Pilotlinie für neuste High-NA-EUV-Lithografie

:quality(80)/p7i.vogel.de/wcms/83/13/8313562301d16a4f35e2aaebb6824fb0/0108771978.jpeg)

Stärkung der japanischen Chipindustrie

Ziel 2-nm-Halbleiter: Imec und Rapidus kooperieren

:quality(80)/p7i.vogel.de/wcms/5e/a7/5ea701db443ba6afeec342ffb8eeb9d2/0105713031.jpeg)

CMOS-Prozesstechnik

1 nm im Blick: Hochtechnologie für tiefe Kontakte auf Nano-Chipstrukturen

Literaturhinweise

[1] ‘Overcoming I/O bottleneck in superconducting quantum computing: multiplexed qubit control with ultra-low-power, base-temperature cryo-CMOS multiplexer’, R. Acharya et al., Nature Electronics;

[2] ‘Comprehensive 300 mm process for Silicon spin qubits with modular integration’, Elsayed et al. 2023 Symposium on VLSI Circuits. IEEE, 2023.

(ID:49784358)

:quality(80)/p7i.vogel.de/wcms/02/46/0246a163cd4f770fc4ec4707eed026a3/0118485226.jpeg)

:quality(80)/p7i.vogel.de/wcms/1d/33/1d33974fef7933ea30c16340eebef3c9/0118272751.jpeg)

:quality(80)/p7i.vogel.de/wcms/de/e9/dee92adb2d0ccca12fc131b4b55a4c51/0118262284.jpeg)

:quality(80)/p7i.vogel.de/wcms/56/3d/563df7482bac59034c2c1ba6949eabeb/0118519606.jpeg)

:quality(80)/p7i.vogel.de/wcms/04/e7/04e7948f02e1d792f245d19fbb6f84be/0118504854.jpeg)

:quality(80)/p7i.vogel.de/wcms/03/c5/03c5925ec95a2630b71e941343a128c5/0118433867.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/76/0d76806079a5a3d36aacdb006a7aba5a/0118407519.jpeg)

:quality(80)/p7i.vogel.de/wcms/7e/bb/7ebbb9e0afa7f66bd9abed55322eb88e/0118350007.jpeg)

:quality(80)/p7i.vogel.de/wcms/0f/89/0f89b224c4b3bb6fda7cbec9c56d9072/0118533982.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/0d/1a0d73826922a88118e8f6e04799665d/0118425986.jpeg)

:quality(80)/p7i.vogel.de/wcms/72/5f/725fbe6121731518e12f6d0b8d7397cd/0118433936.jpeg)

:quality(80)/p7i.vogel.de/wcms/43/a5/43a5630d2a63fbe82f29e17b71d5dcb3/0118499684.jpeg)

:quality(80)/p7i.vogel.de/wcms/74/47/7447ac45f80368ce7f86b76af1c6da99/0118407224.jpeg)

:quality(80)/p7i.vogel.de/wcms/ce/39/ce39569b6845cb072030fdf6505fb7c5/0118404058.jpeg)

:quality(80)/p7i.vogel.de/wcms/c9/22/c9228b8ec955c03dc075e8875f4cabf8/0117754897.jpeg)

:quality(80)/p7i.vogel.de/wcms/07/6f/076f09c7a697f193091a6e6be846aef1/0117862638.jpeg)

:quality(80)/p7i.vogel.de/wcms/30/51/305138abdaeda721646661bf6ac4fdbd/0117756540.jpeg)

:quality(80)/p7i.vogel.de/wcms/3c/b9/3cb980e98baaaadddf69a5dad4ad20a0/0117334644.jpeg)

:quality(80)/p7i.vogel.de/wcms/31/8c/318c8c9e8d61814564d11967ccc14c04/0118494408.jpeg)

:quality(80)/p7i.vogel.de/wcms/eb/6c/eb6c99643aca684c44f5ad0411d71f3f/0118318941.jpeg)

:quality(80)/p7i.vogel.de/wcms/79/4b/794b7d23361d39306753a0abab662274/0117836261.jpeg)

:quality(80)/p7i.vogel.de/wcms/84/64/846421e1abb64717319a401a350ed9ff/0118471925.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/06/b606e1899c3d19b8ac0bf5cdada67cd8/0118340949.jpeg)

:quality(80)/p7i.vogel.de/wcms/42/a0/42a0d035baeb02bf4467dd19ad99f583/0118352721.jpeg)

:quality(80)/p7i.vogel.de/wcms/36/94/36944586a51513ee0dc4cbb1fa410689/0118252602.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/bc/9cbcc8436fa8e226234cebdd1a101d61/0118377191.jpeg)

:quality(80)/p7i.vogel.de/wcms/70/91/7091aed6e9292abc5451815f9499984b/0118509991.jpeg)

:quality(80)/p7i.vogel.de/wcms/08/de/08de3cefb97266232f475bb011d9b0c6/0118162151.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/59/e15978926ae2637c5cc1cb07fc9428a6/0118508628.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/66/c266c5cfbc51fb7d06557ee079d406bf/0116839110.jpeg)

:quality(80)/p7i.vogel.de/wcms/3a/1a/3a1a267224e51b795ccc6b8df959f18e/0115998041.jpeg)

:quality(80)/p7i.vogel.de/wcms/3d/14/3d1447535880e284712d1daba8d7d466/0115848899.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/66/1f/661fa8e004810/heitec-logo-2024-1200px-ae.png)

:fill(fff,0)/p7i.vogel.de/companies/64/21/64219ce08bf52/logo.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/5e/4d/5e4d1371cff23/logo.jpg)

:quality(80)/p7i.vogel.de/wcms/7b/29/7b2955aed10dee65af3720002addd59c/0114003364.jpeg)

:quality(80)/p7i.vogel.de/wcms/c6/55/c655da93949185c35cf92a38bf3e17ae/0116624677.jpeg)