Interview: Chipfertigung mit High-NA-EUV „Die komplexen Probleme der Chipfertigung lassen sich nur gemeinsam lösen“

Anbieter zum Thema

Wie muss sich die Halbleiterindustrie entwickeln, um nicht nur die technologischen Anforderungen zukünftiger Märkte zu erfüllen, sondern gleichzeitig ihre Auswirkungen auf die Umwelt drastisch zu reduzieren? Ein Gespräch mit Steven Scheer, Senior Vice President Advanced Patterning, Process and Materials bei Imec.

Im Interview mit ELEKTRONIKPRAXIS erklärt Steven Scheer, Senior Vice President von Advanced Patterning, Process and Materials bei Imec, die Herausforderungen und Innovationen, die den Bereich der Strukturierung (Patterning) von Substraten in der Chipfertigung kurz- und langfristig prägen werden. Kernkomponenten dabei sind die breite Einführung der Extrem-Ultraviolett-Lithografie (EUVL) mit hoher NA, das Aufkommen neuer Konzepte für Speicher- und Logikbauteile und die Notwendigkeit, die Umweltauswirkungen der IC-Herstellung deutlich zu reduzieren.

Gemeinsam mit ASML, dem bis dato weltweit einzigen Hersteller von EUV-Scannern, baut Imec derzeit eine High-NA-EUV-Pilotanlage in Antwerpen auf. Darin kommt der weltweit erste verfügbare High-NA-Scanner zum Einsatz. Gemeinsam errichten die Partner zudem das High NA EUV Lab, das den Hauptakteuren des Ökosystems eine effektive Kooperationsplattform bieten soll. Denn Scheer ist überzeugt: Nur wenn alle Player – vom Materialhersteller über Maschinenbauer bis hin zum Chiphersteller – zusammen an einem Strang ziehen, sind die vielfältigen und schwierigen Probleme auf dem Gebiet der Chipfertigung zu meistern. Das Labor soll die schnellstmögliche industrielle Einführung und den Ramp-up der High NA EUV-Lithografie erleichtern.

Herr Scheer, das Patterning, also die lithografische Strukturierung von Wafersubstraten, ist der zentrale Prozessschritt in der Chipfertigung. Was tut sich hier, und was ist in den nächsten zwei Jahren zu erwarten?

Steven Scheer: Die Extrem-Ultraviolett-Lithografie, kurz EUVL, ist seit 2019 in der Großserienproduktion von Logikchipproduzenten im Einsatz. Auch Unternehmen für dynamischen, wahlfreien Zugriffsspeicher, den DRAMs, sind zunehmend an der Einführung von EUVL interessiert. Dies konnte nur dank des enormen Einsatzes und Engagements von ASML geschehen: Mit seinen Lithografie-Scannern hat ASML die Grenzen der Technologie weit über das hinausgeschoben, was viele für möglich hielten. Die nächste Evolutionsstufe ist die Einführung von EUVL mit hoher Numerischer Apertur von 0,55, kurz High NA 0,55. Damit ist es möglich, Half-Pitch-Imaging bis hinunter zu 8 Nanometer zu ermöglichen.

Imec und ASML richten ein High NA EUV Lab ein, also eine Pilotlinie für diese Technik. Damit unterstützen wir ihre Einführung: Chipherstellern erhalten frühzeitig die Möglichkeit, mit High NA EUVL zu experimentieren und ihre Prozesse auf Basis dieser Technik zu entwickeln. Gleichzeitig arbeiten wir mit Anbietern von Strukturierungsanlagen und -materialien zusammen, die zum Ökosystem gehören. So bereiten wir EUV-Resistmaterialien, Unterschichten, Trockenätzung, Fotomasken, Auflösungsverbesserungstechniken (RET) und Messtechniken für das High NA EUV Lab vor.

Was werden denn die nächsten Schritte bei der Einführung von High-NA-Lithografie sein?

Oberste Priorität hat die Verfügbarkeit von High-NA-Systemen. ASML und Zeiss machen enorme Fortschritte bei der Integration aller Module und optischen Komponenten. Viele der bahnbrechenden Entwicklungen wurden zu prozessbezogenen Aspekten für die Einführung von EUV mit niedriger NA entwickelt. Daher sind weitere Innovationen erforderlich, um EUV mit hoher NA effektiv einzuführen.

Neben dem High-NA-Tool hat die Entwicklung von EUV-Fotoresisten weiterhin eine sehr hohe Priorität von Imec in Zusammenarbeit mit unseren Ökosystempartnern. High NA EUVL wird die Auflösung erneut verbessern, so dass noch kleinere Strukturgrößen als bisher möglich sein werden – trotz geringerer Tiefenschärfe. Dies führt zu einer Verringerung der Schichtdicke, was die Implementierung neuer Resists und Unterschichten erfordert, um die EUV-Absorption und den Mustertransfer beim Ätzen zu optimieren.

„Wir müssen die Auswirkungen der Stochastik minimieren“

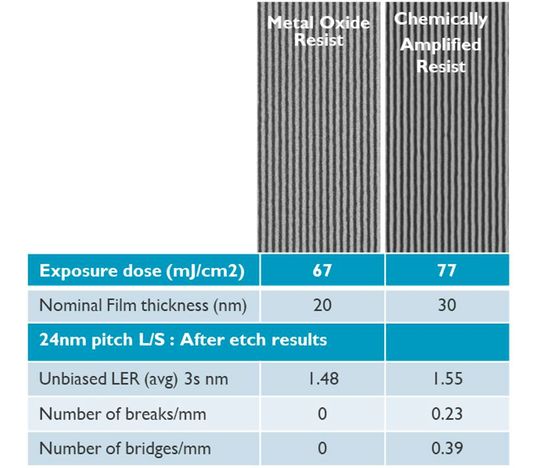

Darüber hinaus müssen wir eine kontinuierliche Verbesserung der stochastischen Rauheit und im Extremfall sogar Ausfälle bei EUV-strukturierten Fotolacken vorantreiben – ein Phänomen, das wir vor ein paar Jahren entdeckt haben. Historisch gesehen wird die Leistung der Fotolackstrukturierung durch die Auflösung, die Linienkantenrauheit (LER) oder die lokale CD-Uniformität (LCDU) und die Empfindlichkeit ausgedrückt – auch bekannt als die RLS-Parameter.

Angesichts der Bedeutung, die der Stochastik beigemessen wird, wird die Strukturierungsleistung heute bereits im frühen Entwicklungsstadium mit einem vierten Parameter, dem Ausfall, bewertet. Dieser spiegelt die durch die Stochastik begrenzte Prozessfenstergröße wider. Wir sind davon überzeugt, dass es Lösungen gibt, die die von den Fotolacksystemen verursachten stochastischen Fehler abschwächen und das Prozessfenster vergrößern, während gleichzeitig die Dosis gesenkt wird. Gemeinsam mit unseren Partnern wollen wir diese neuen Technologien im High NA EUV Lab demonstrieren.

Die Verringerung der Strukturgröße und der Lackdicke wird sich auch auf die Messtechnik auswirken. Neben der Printing-Performance kann sich die drastische Verkleinerung der Abmessungen auch negativ auf die Genauigkeit und Präzision und damit auf die Mess- und Prüfleistung auswirken.

Sie sprechen Fotolacke und -resistsysteme an: Stellt die EUV-Technik besondere Anforderungen daran? Welche Rolle spielt Imec in diesem Zusammenhang?

Um die Probleme zu lösen, die durch die chemische Stochastik – das ist eine andere Stochastik als der sogenannte Shot Noise – entstehen, die durch herkömmliche gemischte Mehrkomponenten-Fotoresistsysteme verursacht werden, werden neue Materialien entwickelt. Beispiele hierfür sind metallhaltige Resists oder Einkomponentenresists. Das Imec unterstützt die Materiallieferanten bei der Entwicklung neuer Konzepte und bei der Bewertung kritischer Aspekte wie Kontaminationsrisiken und Herausforderungen bei der Prozessintegration.

Neuartige EUV-Resistsysteme mit hoher NA können nicht in isolierten Silos entwickelt werden: Eine gemeinsame Optimierung mit technischen Unterschichten, neuartigen Hartmasken und hochselektiven Ätzprozessen ist erforderlich, um die beste Leistung zu erzielen. Imec hat dafür eine neue Toolbox entwickelt, die dabei helfen soll, die Eigenschaften von Resist und Underlayern aufeinander abzustimmen. Durch Material-Screening, Studien zur Anpassung der Oberflächenenergie, physikalische Materialcharakterisierung und Interface-Engineering können aufgeschleuderte oder abgeschiedene Unterlagsschichten zusammen mit dem Fotolack entwickelt werden. Ziel ist es, die Skalierung der EUV-Strukturierung mit optimierter LER, Empfindlichkeit und Defektivität zu ermöglichen.

„Einblicke in das Verhalten von Resisten und Unterschichten unter EUV-Belichtung“

Wir haben eine Infrastruktur zur Charakterisierung von Strukturierungsmaterialien eingerichtet, die wir Attolab nennen. Sie hilft uns, weitere Einblicke in das Verhalten von Resisten und Unterschichten unter EUV-Belichtung zu erhalten und die Materialentwicklung zu beschleunigen. Heute können der Absorptionskoeffizient und die schichtaufgelösten strukturellen Eigenschaften von dünnen Schichten und Stapeln mit Radiometrie und Reflektometrie untersucht werden, Techniken, die den Partnern im Attolab zur Verfügung stehen.

Je kleiner die zu belichtenden Strukturen, desto größer ist der Einfluss der Masken auf das Ergebnis. Welche Entwicklungen sind hier zu beobachten?

In der Entwicklung von Fotomasken gibt es mehrere neue Entwicklungen. Um die EUV-Belichtungsdosis zu senken, werden Masken mit sogenannten Low-n-Absorbern intensiv untersucht, da sie Luftintensitätsprofile mit hohem Kontrast (oder NILS) bei niedriger Belichtungsdosis erzeugen. Bei Imec sind wir auch besorgt über die Stochastik der Wafer und die 3D-Effekte der Maske – das heißt Verzerrungen des Luftbildes, die mit der 3D-Topographie der Maske zusammenhängen. Stochastische Ausfälle auf Waferebene haben viele Ursachen, von denen die Maskenvariabilität eine ist. Um dieses Problem anzugehen, untersuchen wir, welche Arten von Maskenvariabilität einschließlich unterschiedlicher Rauheit anfälliger für erhöhte Stochastik auf Waferebene sind. Ziel ist, aktualisierte Masken- und Blank-Spezifikationen vorzuschlagen.

Außerdem werden EUVL-Scanner mit hoher NA anamorphe Linsen verwenden, die eine ungleiche Vergrößerung in x- und y-Richtung bieten. Diese Anamorphose erfordert ein Field Stitching auf Waferebene, um die gleiche Feldgröße wie bei der herkömmlichen optischen Lithographie zu erreichen. Beim Wafer Field Stitching kommt der Qualität der Maskenfeldkante und möglichen Abhilfemaßnahmen auf Maskenebene größere Bedeutung zu.

Da ein tiefes Verständnis der Wechselwirkungen zwischen Maske und EUV-Beleuchtung immer wichtiger wird, haben wir bei Imec das gesamte Ökosystem der Maskenforschung und -entwicklung zusammengeführt. Gemeinsam mit unseren Masken- und Rohlingslieferanten unterstützen wir die Industrialisierung von Maskeninnovationen, etwa neuartige Absorber, und erforschen die Komplexität von Masken, zum Beispiel Variabilität oder Stitching, sowohl im Imec-ASML High NA EUV Lab als auch durch Modellierung.

„Es gibt keinen grundsätzlichen Hinderungsgrund für die Einführung von High NA EUVL“

Keines dieser Probleme ist ein grundsätzlicher Hinderungsgrund für die Einführung von High NA EUVL. Für eine reibungslose, rechtzeitige und kosteneffiziente Einführung von High NA EUV mit maximaler Leistung ist es jedoch von entscheidender Bedeutung, diese Herausforderungen proaktiv anzugehen und den Hauptakteuren des Ökosystems eine effektive Kooperationsplattform zu bieten. Die Hauptmotivation von Imec und ASML für die Einrichtung dieses High NA EUV-Labors, das um den ersten High NA-Scanner herum aufgebaut ist, besteht darin, die schnellstmögliche industrielle Einführung und den Ramp-up der High NA EUV-Lithografie zu erleichtern.

Der FinFET ist heute das Arbeitstier für die Fertigung von Logikchips, doch neue Transistorkonzepte stehen längst in den Startlöchern. Was ist in den nächsten zwei bis fünf Jahren zu erwarten? Und was bedeutet dies für das Patterning?

Neben den Innovationen im Bereich EUVL ergeben sich einzigartige Möglichkeiten für die Strukturierung durch die Entwicklung neuer Bauelementekonzepte für Logik und Speicher, die zunehmend die dritte Dimension nutzen.

Der komplementäre FET, kurz CFET, ist die künftige Bauelemente-Architektur, die über die Gate-All-Arround-GAA-Nanosheets hinausgeht. CFET verfolgt das Konzept, einen FET-Kanal auf einen anderen FET-Baustein zu stapeln. Die Herstellung der Bauelemente erfordert Strukturierungsschritte mit hohem Aspektverhältnis, um den aktiven Teil, das Gate, die Source-/Drain-Vertiefung sowie die M0A-Kontaktbildung in der Mitte der Leitung zu realisieren. Außerdem sind große Mengen an Materialaussparungen, wie Metall oder Dielektrikum, erforderlich. Innovationen wie die Bottom-up-Abscheidung oder die flächenselektive Abscheidung, kurz ASD, könnten eine wichtige Rolle bei der Reduzierung der Prozesskomplexität für CFET spielen. Um eine Skalierung der CFET-basierten Standardzellen von 5-Tracks auf 4-Tracks zu ermöglichen, wird das CFET-Bauelement wahrscheinlich mit einer rückseitigen Stromzufuhr integriert werden. Dieses neue Routing-Schema erfordert ein hohes Aspektverhältnis der Via-Öffnung und eine selbstausrichtende Strukturierung mit guter Selektivität für den Gate-Spacer.

Aufbruch in die dritte Dimension: 2D-DRAM wird an grundsätzliche Materialgrenzen stoßen

Im Speicherbereich basiert DRAM derzeit auf einem schmalen, hohen Kondensator als Bit-Zelle. Wenn der Pitch skaliert wird, um die Dichte zu erhöhen, wird die seitliche kritische Abmessung, kurz CD, des Kondensators weiter schrumpfen und der Kondensator muss immer höher werden, um die Kapazität konstant zu halten. Dies führt nicht nur zu Fertigungsproblemen und Ertragseinbußen, sondern wir erwarten auch, dass 2D-DRAM an grundlegende Materialgrenzen stoßen wird. Um diese Probleme zu überwinden, werden verschiedene 3D-DRAM-Entwicklungen in Betracht gezogen, und die wichtigsten Herausforderungen werden auf Modulebene angegangen.

Wir werden wahrscheinlich die Einführung neuer Materialien wie Halbleiteroxide erleben, ergänzt durch den Einsatz mehrerer Ätzschritte mit hohem Aspektverhältnis und seitlichen Aussparungen, die in vielerlei Hinsicht eine Herausforderung darstellen. Darüber hinaus dürfte das Füllen der vertikalen Löcher und der seitlichen Hohlräume mit Liner, Dielektrika und Metallen mindestens so anspruchsvoll sein wie heute bei der 3D-NAND-Flash-Technologie.

Da Ihr Team praktisch alle verfahrens- und materialbezogenen Forschungen am Imec durchführt, kommen wir zu einem anderen Thema: Wie trägt das Imec zu einer nachhaltigeren Produktion bei?

Heute macht die IC-Herstellung schätzungsweise 0,1 Prozent der weltweiten Emissionen aus. Aufgrund der zunehmenden Komplexität fortschrittlicher Technologieknoten wird sich der mit der Herstellung von Logiktechnologien verbundene CO2-Ausstoß in den nächsten 10 Jahren jedoch voraussichtlich verdoppeln. Gleichzeitig wird das Gesamtvolumen der produzierten Wafer voraussichtlich um etwa acht Prozent pro Jahr zunehmen. Wenn wir nichts unternehmen, werden sich die mit der IC-Herstellung verbundenen Emissionen im nächsten Jahrzehnt vervierfachen. Gemäß dem Pariser Abkommen sollen alle Industriesektoren ihre Emissionen in jedem Jahrzehnt halbieren. Mit anderen Worten: Im Szenario des „Nichtstuns“ wird unsere Branche um den Faktor acht vom Ziel abweichen.

Nichtstun ist keine Option: Mit der IC-Herstellung verbundene CO2-Emissionen müssen deutlich sinken

Aus diesem Grund ist Nachhaltigkeit ein wichtiger Pfeiler der Forschung von Imec. Wir haben unser Programm für nachhaltige Halbleitertechnologien und -systeme, englisch: Sustainable Semiconductor Technologies and Systems oder SSTS, ins Leben gerufen. Hier setzt sich die gesamte Lieferkette zusammen, um gemeinsam das Ziel zu erreichen, dass bei der Herstellung von Chips keine Emissionen mehr anfallen. Um die Umweltauswirkungen einer generischen Halbleiterfabrik mit hohem Volumen zu quantifizieren, bauen wir eine virtuelle Fabrik auf, Imec.netzero genannt. Die entwickelten Modelle werden durch Partnerschaften mit Ausrüstungs- und Materiallieferanten kontinuierlich überprüft und validiert.

Auf der bevorstehenden SPIE-Konferenz Advanced Lithography and Patterning werden wir eine quantitative Bewertung der Auswirkungen der Strukturierung auf die Kohlenstoffemissionen bei der modernen IC-Fertigung vorstellen. Es wurden Bereiche mit großen Auswirkungen identifiziert, für die wir in unserer eigenen Fabrik Lösungen suchen. Beispiele hierfür sind der geringere Einsatz von fluorierten Ätzgasen, der geringere Wasserverbrauch, das Recycling seltener Materialien, die Rückgewinnung von Wasserstoff und Lithografieprozesse mit geringerer Dosis.

Die Berücksichtigung der Umweltauswirkungen bei der Entwicklung zukünftiger Technologien mag als schwierige, vielleicht sogar entmutigende Aufgabe erscheinen. Das ist sie auch. Aber wir können es schaffen. Unsere Branche ist für ihre Kreativität und Innovation bekannt, und jetzt kommt ein weiteres Entwicklungsziel hinzu: die Verringerung der Umweltauswirkungen. (me)

Steven Scheer

Steven Scheer

Steven Scheer wurde 2022 zum Senior Vice President von Advanced Patterning, Process and Materials (APPM) bei Imec ernannt, nachdem er 2019 als Vice President von APPM zu Imec kam. Zu seinen Aufgaben gehören Patterning, Unit Process und die Entwicklung neuer Materialien für Logik, Speicher, Fotonik und 3D-Integration.

Zuvor war er als Account Technology Director bei Tokyo Electron Ltd. (TEL), wo er für Kunden in der Region Portland OR zuständig war. Bei TEL war er 13 Jahre lang für Forschung und Entwicklung in den Bereichen Strukturierung und Reinigung zuständig, einschließlich Managementfunktionen in den USA sowie im TEL-Werk in Kumamoto, Japan, und in der Forschungs- und Entwicklungsabteilung des Unternehmens in Tokio.

Er begann seine Forschungskarriere bei IBM in Fishkill, New York, wo er an der Entwicklung von Mustern für 90 und 65 nm arbeitete. Er hat einen Doktortitel in Chemieingenieurwesen von der University of Texas in Austin.

Bildquelle: Imec

:quality(80)/p7i.vogel.de/wcms/c3/46/c346a009d8e2cf99408954492b046558/0112553950.jpeg)

Von Europa in die Welt

Modernste Chipfertigung: Imec und ASML bauen Pilotlinie für neuste High-NA-EUV-Lithografie

:quality(80)/p7i.vogel.de/wcms/5e/a7/5ea701db443ba6afeec342ffb8eeb9d2/0105713031.jpeg)

CMOS-Prozesstechnik

1 nm im Blick: Hochtechnologie für tiefe Kontakte auf Nano-Chipstrukturen

:quality(80)/p7i.vogel.de/wcms/e2/51/e251e91d82f8873e3629ecb95b442913/0107502579.jpeg)

Alternative Verbindungsmaterialien gesucht

IC-Fertigung im Ångström-Bereich: Ende der Kupfer-Ära?

:quality(80)/p7i.vogel.de/wcms/15/93/159301668fb8240a9fc545392f8943f9/0105943805.jpeg)

Energieeffizientes Design

Neuartiger Neuro-Chip nutzt direkte Digitalisierung

(ID:49603221)

:quality(80)/p7i.vogel.de/wcms/02/46/0246a163cd4f770fc4ec4707eed026a3/0118485226.jpeg)

:quality(80)/p7i.vogel.de/wcms/1d/33/1d33974fef7933ea30c16340eebef3c9/0118272751.jpeg)

:quality(80)/p7i.vogel.de/wcms/de/e9/dee92adb2d0ccca12fc131b4b55a4c51/0118262284.jpeg)

:quality(80)/p7i.vogel.de/wcms/56/3d/563df7482bac59034c2c1ba6949eabeb/0118519606.jpeg)

:quality(80)/p7i.vogel.de/wcms/04/e7/04e7948f02e1d792f245d19fbb6f84be/0118504854.jpeg)

:quality(80)/p7i.vogel.de/wcms/03/c5/03c5925ec95a2630b71e941343a128c5/0118433867.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/76/0d76806079a5a3d36aacdb006a7aba5a/0118407519.jpeg)

:quality(80)/p7i.vogel.de/wcms/7e/bb/7ebbb9e0afa7f66bd9abed55322eb88e/0118350007.jpeg)

:quality(80)/p7i.vogel.de/wcms/0f/89/0f89b224c4b3bb6fda7cbec9c56d9072/0118533982.jpeg)

:quality(80)/p7i.vogel.de/wcms/1a/0d/1a0d73826922a88118e8f6e04799665d/0118425986.jpeg)

:quality(80)/p7i.vogel.de/wcms/72/5f/725fbe6121731518e12f6d0b8d7397cd/0118433936.jpeg)

:quality(80)/p7i.vogel.de/wcms/43/a5/43a5630d2a63fbe82f29e17b71d5dcb3/0118499684.jpeg)

:quality(80)/p7i.vogel.de/wcms/74/47/7447ac45f80368ce7f86b76af1c6da99/0118407224.jpeg)

:quality(80)/p7i.vogel.de/wcms/ce/39/ce39569b6845cb072030fdf6505fb7c5/0118404058.jpeg)

:quality(80)/p7i.vogel.de/wcms/c9/22/c9228b8ec955c03dc075e8875f4cabf8/0117754897.jpeg)

:quality(80)/p7i.vogel.de/wcms/07/6f/076f09c7a697f193091a6e6be846aef1/0117862638.jpeg)

:quality(80)/p7i.vogel.de/wcms/30/51/305138abdaeda721646661bf6ac4fdbd/0117756540.jpeg)

:quality(80)/p7i.vogel.de/wcms/3c/b9/3cb980e98baaaadddf69a5dad4ad20a0/0117334644.jpeg)

:quality(80)/p7i.vogel.de/wcms/31/8c/318c8c9e8d61814564d11967ccc14c04/0118494408.jpeg)

:quality(80)/p7i.vogel.de/wcms/eb/6c/eb6c99643aca684c44f5ad0411d71f3f/0118318941.jpeg)

:quality(80)/p7i.vogel.de/wcms/79/4b/794b7d23361d39306753a0abab662274/0117836261.jpeg)

:quality(80)/p7i.vogel.de/wcms/84/64/846421e1abb64717319a401a350ed9ff/0118471925.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/06/b606e1899c3d19b8ac0bf5cdada67cd8/0118340949.jpeg)

:quality(80)/p7i.vogel.de/wcms/42/a0/42a0d035baeb02bf4467dd19ad99f583/0118352721.jpeg)

:quality(80)/p7i.vogel.de/wcms/36/94/36944586a51513ee0dc4cbb1fa410689/0118252602.jpeg)

:quality(80)/p7i.vogel.de/wcms/9c/bc/9cbcc8436fa8e226234cebdd1a101d61/0118377191.jpeg)

:quality(80)/p7i.vogel.de/wcms/70/91/7091aed6e9292abc5451815f9499984b/0118509991.jpeg)

:quality(80)/p7i.vogel.de/wcms/08/de/08de3cefb97266232f475bb011d9b0c6/0118162151.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/59/e15978926ae2637c5cc1cb07fc9428a6/0118508628.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/66/c266c5cfbc51fb7d06557ee079d406bf/0116839110.jpeg)

:quality(80)/p7i.vogel.de/wcms/3a/1a/3a1a267224e51b795ccc6b8df959f18e/0115998041.jpeg)

:quality(80)/p7i.vogel.de/wcms/3d/14/3d1447535880e284712d1daba8d7d466/0115848899.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/64/21/64219ce08bf52/logo.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/5e/4d/5e4d1371cff23/logo.jpg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/125700/125709/65.png)

:quality(80)/p7i.vogel.de/wcms/9f/46/9f460c7001f06a93711752ef6c72db37/0113730852.jpeg)

:quality(80)/p7i.vogel.de/wcms/c3/46/c346a009d8e2cf99408954492b046558/0112553950.jpeg)