Halbleiter-Ökosystem Die Ära CMOS 2.0: Was sich hinter der CMOS-Revolution verbirgt

Anbieter zum Thema

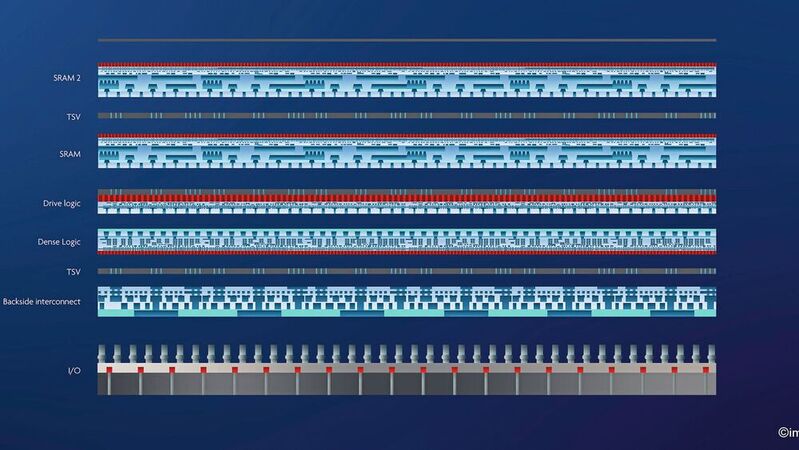

Die CMOS-Technik ist nahezu ausgereizt. Ein neues Paradigma, genannt CMOS 2.0, wird durch Systemtechnologie-Co-Optimierung (STCO) getrieben und bringt Heterogenität in das Innere des SoCs. So werden maßgeschneiderte Chips möglich, die aus einer intelligenten Partitionierung der verschiedenen Funktionen in mehreren gestapelten 3D-Schichten bestehen.

Ein universell verwendbares Design und kontinuierliche Miniaturisierung waren der Schlüssel zum Erfolg von CMOS. Die jüngste Explosion der Leistungsanforderungen in immer mehr Architekturen und Anwendungen findet jedoch zu einer Zeit statt, in der CMOS vor beispiellosen Herausforderungen hinsichtlich Skalierung und Kosten steht. Daher müssen wir das bestehende Paradigma neu überdenken.

Die CMOS-Technologie hat die Elektronikindustrie revolutioniert, wobei sie Leistung, Energieeffizienz und niedrige Kosten in Einklang gebracht hat. Das System-on-a-Chip (SoC)-Paradigma hat es ermöglicht, immer komplexere Systeme mit einem universellen Ansatz zu realisieren und eine immer größere Anzahl von Transistoren auf einem einzigen Chip zu integrieren. Dies ermöglichte auch eine preiswerte Massenproduktion, wodurch die Elektronik erheblich preiswerter wurde, wie es der verstorbene Gordon Moore vor über einem halben Jahrhundert vorausgesagt hatte.

:quality(80)/images.vogel.de/vogelonline/bdb/1350600/1350675/original.jpg)

Warum der Transistor zweimal erfunden wurde

Moore erklärte, dass sich die Anzahl der Transistoren auf einem Halbleiterchip alle zwei Jahre verdoppeln würde, ein Trend, der die Entwicklung von immer leistungsfähigeren und effizienteren elektronischen Geräten vorantreiben würde. Einfach ausgedrückt: Man macht Dinge besser, indem man sie kleiner macht.

Beyond Moore

Die von Dennard et. al. 1974 erstmals beschriebenen Skalierungsprinzipien für Polysilizium-Gate-MOSFETs lieferten den Fahrplan für die kontinuierliche Verbesserung der Schaltgeschwindigkeit von Transistoren bei konstanter Leistungsdichte bis in die frühen 2000er Jahre [1]. Grenzen der Leistungssteigerung durch die Skalierung der Gatelänge und des Gate-Oxids wurden durch Verbesserungen der Kanalbeweglichkeit durch den Einsatz von Stressoren und High-k-Dielektrika kompensiert.

Tri-Gate-Strukturen von finFETs und Gate-Allaround-Nanosheet-Bausteinen ermöglichten eine weitere Skalierung der Gatelänge, allerdings deutlich weniger als das Paradigma der konstanten Leistungsdichte in der Dennard-Ära. Die Erhöhung der Energiedichte führte zum Übergang zu Multi-Core-Architekturen.

Diese enorme Konzentration auf Miniaturisierung und Universal-Design war ausschlaggebend für den enormen Erfolg von CMOS in den letzten Jahrzehnten, stößt aber heute an seine physikalischen Grenzen.

CMOS-Skalierung stößt auf diverse Hürden

Während der SoC-Ansatz maximale Energieeffizienz bietet, hat er die Systemarchitekten dazu gebracht, eine Vielzahl komplexer Funktionen innerhalb der CMOS-Plattform zu akkumulieren. Die Optimierung von Multi-Core-Architekturen, die in den 2000er Jahren entstanden ist, hat zu einer breiten Vielfalt von Computing-Engines geführt, von der ersten Trennung zwischen CPU und GPU über diverse energieoptimierte Prozessoren bis hin zu speziellen Arten von Beschleunigern. Auch das Speichersubsystem innerhalb des SoC hat sich im Laufe der Jahre stark diversifiziert, was zu komplexen Hierarchien und einer Vielzahl von Zugriffsmechanismen geführt hat.

Die treibende Kraft hinter dieser kontinuierlichen Optimierung ist die Notwendigkeit, den jeweiligen Rechner auf die Art der auszuführenden Aufgaben bzw. Arbeitslasten zu optimieren, die jeweils sehr spezifisch für die Zielanwendung sind. Es ist bemerkenswert, dass eine solche Entwicklung innerhalb einer einzigen technologischen Plattform überhaupt möglich war, wobei mehrere wesentliche Hindernisse die weitere Entwicklung behindern:

- Wir sehen große Fortschritte bei den elektrischen Chip-zu-Chip-Verbindungen, ermöglicht durch die Skalierung der Pitches von Micro-Bumps und Hybrid Bonding, die eine feinkörnige Partitionierung von SoC-Funktionen ermöglichen. Fortschritte bei optischen Verbindungen auf der Basis von Si-Photonik und 3D-Verbindungen ermöglichten Co-Packaging, das optische Konnektivität mit hoher Bandbreite und geringem Stromverbrauch bei erheblich geringerer Länge bietet. Dies wirft die Frage auf, ob ein SoC-Ansatz noch seinen ursprünglichen Energieeffizienzvorteil hat. Eine Aufteilung in mehrere Dies könnte große Vorteile bei der Kosten- und Leistungsoptimierung bieten.

- Die Vielfalt der Anwendungen, die fortschrittliche Technologien erfordern, um die Grenzen der Computerleistung zu verschieben, bringt CMOS an die Grenzen dessen, was es als allgemeine Plattform bieten kann. Die Entwickler müssen nun die Einschränkungen der einzelnen Plattform umgehen, was zu Ineffizienz führen kann.

- Ganzheitliche Skalierungslösungen für die komplette CMOS-Plattform werden immer schwieriger. Bei der 2-nm-Nanosheet-Technologie zum Beispiel werden die traditionellen Dickoxid-IO-Schaltungen aus dem SoC verdrängt. Das SRAM skaliert nicht so stark wie die Logik, und der Strom im SoC muss über ein rückseitiges Verbindungsnetzwerk verteilt werden, da der Widerstand auf der Vorderseite der Verbindungen zu groß wäre.

- Die Steigerung der Knoten-zu-Knoten-Leistung bei CMOS hat sich ebenfalls drastisch verringert, da die RC-Parasitika der Transistoren schneller zunehmen als die Ansteuerungsstärke. Dies geschieht zu einer Zeit, in der die Design- und Wafer-Kosten für fortschrittliche CMOS aufgrund der Komplexität der Designregeln und der Prozessintegration erheblich steigen.

Von der Allzweckwaffe zur Lotterie

In diesem interessanten Kontext der sich ändernden Technologie- und Produktanforderungen haben kreative Kombinationen zu innovativen Lösungen geführt. Der Apple M1 Ultra beispielsweise verbindet zwei Chips über eine Siliziumbrücke miteinander und schafft so ein hybrides SoC mit noch nie dagewesener Leistung und Fähigkeiten [2].

AMD erhöht die Speicherkapazität, indem es einen SRAM-Die in 3D auf das ursprüngliche Prozessor-SoC stapelt [3]. Im Bereich der Künstlichen Intelligenz (KI) stoßen super skalierte Verarbeitungssysteme wie der Full Wafer WSE-2 von Cerebras und der große GPU-Die H100 von Nvidia in Kombination mit HBM DRAM an die Grenzen des Deep Learning Computing [4,5].

Die obigen Beispiele veranschaulichen, wie die technische Entwicklung in Abhängigkeit von den spezifischen Anforderungen eines bestimmten Anwendungsbereichs in die Extrembereiche getrieben wird. Gleichzeitig werden neue Anwendungen wie Augmented und Virtual Reality, 6G Wireless und autonome Fahrzeuge extreme Leistungssteigerungen und Energieeinsparungen erfordern. Die Arbeitsbelastung und die Betriebsbedingungen werden die Vielfalt der Implementierungen, die CMOS voraussichtlich unterstützen wird, noch weiter erhöhen und viele weitere suboptimale Kompromisse erzwingen.

Mit anderen Worten: Wir erleben, dass CMOS seine einst so mächtige Rolle als Allzwecktechnologie nicht mehr erfüllen kann. Stattdessen werden wir in eine Situation geraten, in der der Erfolg einer Anwendung davon abhängt, wie gut der verfügbare CMOS seine spezifischen Randbedingungen erfüllt. Sara Hooker hat dies als 'Hardware-Lotterie' bezeichnet und damit angedeutet, dass die Hardware darüber entscheidet, welche Forschungsideen erfolgreich sein oder scheitern werden [6].

Ko-Optimierung von System und Technologie

„Wenn das einzige Werkzeug, das man hat, ein Hammer ist, ist man versucht, jedes Problem wie einen Nagel zu behandeln“ (A. Maslow). Der einzige Ausweg aus diesem Dilemma besteht darin, den Werkzeugkasten zu erweitern. Mit anderen Worten, wir brauchen Technologieplattformen, die vielseitiger sind, denn die Zwänge – Energie, Kosten, Temperatur, Leistungsdichte, Speicherkapazität, Geschwindigkeit – für mobile Chipsätze beispielsweise sind ganz andere als für HPC- oder VR-Systeme.

:quality(80)/p7i.vogel.de/wcms/3d/e1/3de1821bfd390e21d05286204f4f29ad/0102645955.jpeg)

Probleme in der Chipfertigung

Chipevolution in sechs Wellen: Moore’s Law auf dem Prüfstand

Es ist schwer vorstellbar, dass wir mit einer Plattform weitermachen, die immer weiter skaliert und dennoch all diesen Anforderungen gerecht wird. Deshalb stellen wir uns ein völlig neues Paradigma vor, CMOS 2.0, angetrieben durch Systemtechnologie-Co-Optimierung (STCO). Bei der STCO arbeiten die Systementwickler eng mit den Technologie-Teams zusammen, um die am besten geeigneten Optionen zu ermitteln, anstatt sich auf Skalierungsoptionen von der Stange zu verlassen. Die Technologie-Spezialisten müssen bei der Entwicklung von Angeboten der nächsten Generation auch die spezifischen Systemspezifikationen kennen. Die Vielfalt der Anwendungen, Arbeitslasten und Systembeschränkungen erfordert eine breitere Palette von Technologieoptionen.

Dies erfordert ein Umdenken bei der Technologieplattform, so dass sie die Anforderungen einer Vielzahl von Systemen und Anwendungen abdeckt. CMOS 2.0 erreicht dies, indem es maßgeschneiderte Chips ermöglicht, die aus einer intelligenten Partitionierung der verschiedenen Funktionen in mehreren gestapelten 3D-Schichten bestehen.

CMOS 2.0: Das Beste aus beiden Welten

CMOS 2.0 wird bestehende und neue fortschrittliche 2,5D- und 3D-Verbindungstechnologien wie Dense Pitch Cu Hybrid Bonding, dielektrisches Bonding, Chiplet-Integration, Wafer-Back-Side-Processing sowie sequentielle 3D-Integration mit heterogenem Schichttransfer nutzen. Die hohe Granularität der SoC-Verbindungen und die große technologische Heterogenität, die das System in einem Gehäuse bietet, werden es ermöglichen, die Beschränkungen des herkömmlichen CMOS zu überwinden.

CMOS 2.0 wird die Verwendung von Transistoren mit niedriger Kapazität und geringem Leistungsbedarf zur Steuerung von Kurzstreckenverbindungen ermöglichen, während Transistoren mit hohem Leistungsbedarf in einer separaten Schicht zur Steuerung von Fernverbindungsstellen eingesetzt werden. Neue integrierte Speicher könnten als separate Schicht in der Cache-Hierarchie eingeführt werden.

Dies wird auch extreme BEOL-Pitch-Muster für die Skalierung ermöglichen, ohne dass der Spannungsabfall bei der Stromversorgung ein Problem darstellt. Es wird einfacher werden, Nicht-Silizium-Bauteile wie 2D-Materialien, neuartige eingebettete Speicher wie MRAM oder Halbleiter mit aufgedampften Oxiden einzuführen, da sie nicht mehr die CMOS-Spezifikationen für allgemeine Anwendungen erfüllen müssen. Für Entwickler wird sich die CMOS-2.0-Plattform wie herkömmliches CMOS anfühlen, jedoch mit einer deutlich erweiterten und vielseitigeren Toolbox.

Auch wenn die Skalierung der Dimensionen nicht mehr die alleinige Antwort auf die Skalierung von Computern ist, wird CMOS 2.0 die Anforderungen an eine höhere Dichte nicht beseitigen. Das Skalierungsproblem muss jedoch auf ganzheitliche Weise angegangen werden, da die Antwort je nach Anwendung unterschiedlich ausfallen wird. Logik mit hoher Dichte wird die Leistung pro Watt optimieren, während Logik mit hohem Durchsatz die Bandbreite und Leistung im kritischen Pfad beibehält.

Bausteine, die sich nicht so gut skalieren lassen, wie z. B. dichte Schaltlogiken, wie z. B. Thick-Oxide IO, Power Switches, Analog- oder MIMCAPs, können auf einer separaten Schicht mit einem kostengünstigeren Technologieknoten integriert werden. Der Wegfall aller SoC-Bauteile, die zwar unverzichtbar, aber nicht skalierbar waren, öffnet auch die Tür zu einer Reihe von neuen Komponentenarten.

Die CMOS-Revolution ist bereits in vollem Gang

Stromverteilungsnetzwerke auf der Wafer-Rückseite sind eines der ersten Anzeichen dafür, dass wir in eine neue CMOS-2.0-Ära eintreten. Alle großen Foundries haben angekündigt, dass sie auf integrierte Chips mit Stromverteilungssystemen auf der Wafer-Rückseite umsteigen werden, die für die Entwicklung leistungsstarker und energieeffizienter elektronischer Bausteine immer wichtiger geworden sind. Der Zugang zur Wafer-Rückseite eröffnet die Möglichkeit, Komponenten wie Leistungsschalter zu integrieren, das globale Clock-Routing von der Vorderseite zu verlagern oder neue Systemfunktionen hinzuzufügen.

Dieser Paradigmenwechsel bietet eine kompliziertere technologische Realität. Wie schnell werden sich die EDA-Tools weiterentwickeln? Werden die Kosten und die Komplexität der Partitionierung zu hoch werden? Wird die Erwärmung von CMOS-2.0-Plattformen beherrschbar sein? Das kann nur die Zeit zeigen. Um den deutschen Philosophen und Revolutionär Friedrich Engels zu zitieren: „Niemand weiß genau, welche Revolution er auslöst.“

Gleichzeitig ist es genau das, was diese Zeiten so faszinierend macht. Diese unbekannten Gebiete zu erkunden, erfordert eine enge Zusammenarbeit und Co-Innovation im gesamten Halbleiter-Ökosystem. Es geht nicht um das Mooresche Gesetz an sich, sondern um die Fähigkeit, wirtschaftliches Wachstum, wissenschaftlichen Fortschritt und nachhaltige Innovation zu ermöglichen. (kr)

Die Orginalveröffentlichung ist in Nature Reviews Electrical Engineering erschienen.

:quality(80)/p7i.vogel.de/wcms/67/f4/67f4c8ff75d1b08047aadadc97adae41/91981451.jpeg)

Halbleiterintegration

Kommentar: Warum das Mooresche Gesetz nicht tot ist

:quality(80)/p7i.vogel.de/wcms/5e/a7/5ea701db443ba6afeec342ffb8eeb9d2/0105713031.jpeg)

CMOS-Prozesstechnik

1 nm im Blick: Hochtechnologie für tiefe Kontakte auf Nano-Chipstrukturen

Literatur

[1] Dennard, R. H. et al. Design of Ion-Implanted MOSFET’s With Very Small Physical Dimensions. IEEE J Solid-State Circuits 9, 256–268 (1974).

[2] Kenyon, C. & Capano, C. Apple Silicon Performance in Scientific Computing. 2022 IEEE High Performance Extreme Computing Conference, HPEC 2022 (2022) doi:10.1109/HPEC55821.2022.9926315.

[3] AMD 3D V-CacheTM Technology | AMD. https://www.amd.com/en/technologies/3d-v-cache.

[4] Lie, S. Cerebras Architecture Deep Dive: First Look Inside the Hardware/Software Co-Design for Deep Learning. IEEE Micro 43, 18–30 (2023).

[5] Choquette, J. NVIDIA Hopper H100 GPU: Scaling Performance. IEEE Micro 43, 9–17 (2023).

[6] Hooker, S. The Hardware Lottery. CoRR abs/2009.06489, (2020).

(ID:49990429)

:quality(80)/p7i.vogel.de/wcms/a4/d1/a4d112808ba72fb31a6c9770d11ef157/0118199593.jpeg)

:quality(80)/p7i.vogel.de/wcms/ef/72/ef721c7df54421ff4f6b911b9f5826e8/0118218658.jpeg)

:quality(80)/p7i.vogel.de/wcms/ed/b3/edb3872e6b2694039a712ba762bf5ea3/0118168079.jpeg)

:quality(80)/p7i.vogel.de/wcms/42/22/42228875afe426c07bd09726de8ce039/0118250473.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/10/d6101a2aac8c7d2cab2ff31546979254/0118103063.jpeg)

:quality(80)/p7i.vogel.de/wcms/29/c2/29c2b968dc07be08e6062d8e6d8c387b/0118061450.jpeg)

:quality(80)/p7i.vogel.de/wcms/90/27/9027f3a201ad0e0eeeecc53846e2a990/0118165202.jpeg)

:quality(80)/p7i.vogel.de/wcms/fe/b1/feb1ceb3750245197d7851df67e05479/0118163169.jpeg)

:quality(80)/p7i.vogel.de/wcms/5f/c6/5fc62a91bffb6c673c36722011f8205c/0118076327.jpeg)

:quality(80)/p7i.vogel.de/wcms/1e/51/1e513481ef401300756c3bb189188c01/0117631502.jpeg)

:quality(80)/p7i.vogel.de/wcms/56/6f/566fa0229f2dbf6aa49dfa4923210b21/0118162056.jpeg)

:quality(80)/p7i.vogel.de/wcms/f3/24/f3245522a3428e1787cd2418d901c62c/0118152080.jpeg)

:quality(80)/p7i.vogel.de/wcms/c9/22/c9228b8ec955c03dc075e8875f4cabf8/0117754897.jpeg)

:quality(80)/p7i.vogel.de/wcms/07/6f/076f09c7a697f193091a6e6be846aef1/0117862638.jpeg)

:quality(80)/p7i.vogel.de/wcms/30/51/305138abdaeda721646661bf6ac4fdbd/0117756540.jpeg)

:quality(80)/p7i.vogel.de/wcms/3c/b9/3cb980e98baaaadddf69a5dad4ad20a0/0117334644.jpeg)

:quality(80)/p7i.vogel.de/wcms/79/4b/794b7d23361d39306753a0abab662274/0117836261.jpeg)

:quality(80)/p7i.vogel.de/wcms/f3/88/f388bad02124a8ac7fc5663627838b69/0117819459.jpeg)

:quality(80)/p7i.vogel.de/wcms/2b/cc/2bccc41bb07c895dda4839b927d8c265/0116514416.jpeg)

:quality(80)/p7i.vogel.de/wcms/36/94/36944586a51513ee0dc4cbb1fa410689/0118252602.jpeg)

:quality(80)/p7i.vogel.de/wcms/1e/5a/1e5a931b4b81371d6761358130476db5/0117914243.jpeg)

:quality(80)/p7i.vogel.de/wcms/f7/a8/f7a8de2339926d03f6309495bb3e3cdf/0117808261.jpeg)

:quality(80)/p7i.vogel.de/wcms/18/32/1832350986a019c0f74079c2fd03fa28/0117909885.jpeg)

:quality(80)/p7i.vogel.de/wcms/02/39/0239f3ad5b99d9cde1e9a269105dac38/0118236281.jpeg)

:quality(80)/p7i.vogel.de/wcms/bf/75/bf75e96d07c11d7e147b16235159c660/0118153476.jpeg)

:quality(80)/p7i.vogel.de/wcms/d0/15/d01573f5c7986989d4fa27fecdb17c32/0118126305.jpeg)

:quality(80)/p7i.vogel.de/wcms/08/de/08de3cefb97266232f475bb011d9b0c6/0118162151.jpeg)

:quality(80)/p7i.vogel.de/wcms/a2/24/a2249bc111c69b9af5404fc356834e9b/0118129754.jpeg)

:quality(80)/p7i.vogel.de/wcms/16/cc/16cc54cea371a36ebef7a53b952f8516/0118069700.jpeg)

:quality(80)/p7i.vogel.de/wcms/15/74/15744e690ff03eef2b863223b28604fd/0118160633.jpeg)

:quality(80)/p7i.vogel.de/wcms/0f/63/0f6307f7514bc193712954c50b80f0f7/0118163432.jpeg)

:quality(80)/p7i.vogel.de/wcms/7d/41/7d4118afaafc06500e8f54ebf6079493/0118116849.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/66/c266c5cfbc51fb7d06557ee079d406bf/0116839110.jpeg)

:quality(80)/p7i.vogel.de/wcms/3a/1a/3a1a267224e51b795ccc6b8df959f18e/0115998041.jpeg)

:quality(80)/p7i.vogel.de/wcms/3d/14/3d1447535880e284712d1daba8d7d466/0115848899.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/5e/e8/5ee8685f55961/duagon-logo-without-r.png)

:fill(fff,0)/p7i.vogel.de/companies/64/21/64219ce08bf52/logo.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/9600/9682/65.jpg)

:quality(80)/p7i.vogel.de/wcms/3b/1c/3b1c7305493c4b0418f3b0cb687d5596/0116895487.jpeg)

:quality(80)/p7i.vogel.de/wcms/f1/ab/f1abe9a0cd1f38e5a3c58d1b48519f4b/0115155854.jpeg)